74HC573透明ラッチ:関数、操作、アプリケーション

74HC573は、シンプルなピンレイアウトと信頼できるデータストレージのため、デジタルサーキットの重要な部分です。この記事では、それがどのように機能し、機能し、どのようにデジタルサーキットの改善に役立つかを説明します。ピンレイアウト、電気特性、および一般的な用途を調べて、データ処理をサポートする方法を示します。カタログ

ラッチを定義するものは何ですか?

ラッチは、他の回路とは異なり、クロック信号を必要とせずに1つの情報を保存するデジタルシステムの一種の回路です。入力信号に基づいてデータを少し安定させ、デジタルメモリの主要な部分にします。いくつかのラッチが連携すると、それぞれ4ビットと8ビットを保存する「4ビットラッチ」または「8ビットラッチ」のようなビットをより多く保持できます。ラッチは、より複雑なメモリシステムの機械スイッチとビルディングブロックのバウンスによって引き起こされるエラーの防止などのアプリケーションで役立ちます。2つの入力で出力を設定およびリセットするSRラッチや、コントロール信号を使用してデータを保持するDラッチなど、いくつかの種類のラッチがあります。適切なラッチを選択することは、必要なこととそれがどこで使用されるかによって異なります。

74HC573チップとは何ですか?

74HC573 8つのD型ラッチを含む高性能CMOSデバイスで、それぞれに独自の入力と3つの状態の出力があります。ラッチイネーブル(LE)および出力ENABLE(OE)端子を使用してこれらのラッチを制御でき、異なる操作で柔軟性を与えることができます。このデバイスは、一般的にデータストレージと処理のためのコンピューティング、情報交換を可能にする通信、および産業制御システムで使用されます。74HC573を使用する場合は、各ラッチがシステム全体にどのように影響するかを考えて検討します。たとえば、コンピューティングでは、処理速度とストレージの信頼性のバランスをとる必要があります。通信では、74HC573のアーキテクチャでサポートされているシームレスなデータ交換に焦点を当てています。産業環境では、その精度により、さまざまな条件で信頼できるパフォーマンスが保証されます。

代替品と同等物

CD4099:CD4099は、ユニークな機能を備えた優れた代替品です。表面的には似ているかもしれませんが、テストは電力使用と応答時間の違いを示しています。

SN74AHCT573DWR:SN74AHCT573DWRは、高速操作で知られているもう1つの適切なオプションであり、時間に敏感なタスクに最適です。この部分をオリジナルと比較すると、設計の強化または調整、速度のバランス、電力使用、および熱管理に役立ちます。

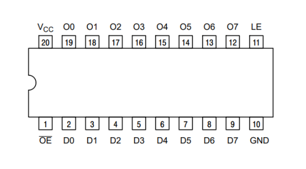

74HC573ラッチピンレイアウト

74HC573ラッチピン機能

•OE(出力を有効にする)

このピンは、出力ピン(q)がアクティブであるかどうかを制御します。オンになると、データはQピンを介して流れる可能性があります。これは、いくつかのデバイスが同じデータラインを共有し、データフローの管理に役立つ場合に役立ちます。

•le(ラッチ有効)

LE PINは、入力ピン(D)からのデータがラッチに保存されると制御します。アクティブ化すると、データがロックされ、ピンが再びアクティブになるまで出力を安定させます。これにより、高速デジタルシステムのデータを安定させるのに役立ちます。

•D0〜D7(データ入力ピン)

これらのピンは、バイナリデータがラッチに入り、複雑な回路での正確なデータタイミングに使用する場所です。

•Q0〜Q7(データ出力ピン)

これらのピンは、ラッチされたデータを出力します。彼らは、マイクロプロセッサのようにデータが時間通りにリリースされることを保証します。

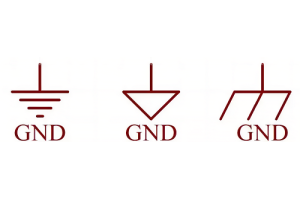

•GND(地上ターミナル)

このピンは地面に接続され、回路を安定させる参照電圧を提供します。

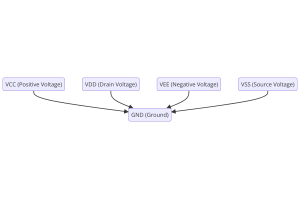

•VCC(供給電圧)

このピンは、ラッチが機能するのに必要な電力を提供します。電圧は、適切に機能するためにデバイスの要件と一致する必要があります。

74HC573ラッチの関数

74HC573ラッチは、合計8つの3ワイヤピンで構成され、2つの異なる4ビットポートに分割されています。各ポートは、独自の入力ピンと出力ピンのセットを備えており、8ビットデータを効率的に処理できます。主な機能は、汎用性と動的なデータ管理を促進する双方向の入力ポートです。また、内部の8ビットメモリは、完全な8ビットバイナリシーケンスを効率的に保存します。

データ処理と処理

74HC573は、データをすばやく処理するのに最適です。これは、TTL互換の入力に対して異なるロジックレベルの原因でうまく機能します。このラッチは、パフォーマンスが多いアプリケーションなどの高速データタスクに効率的に、最大25MHzのパルスを処理できます。その強力な運転能力により、信頼できるデータ送信が保証されます。

高速変換および保護メカニズム

74HC573は、高速データ変換に最適です。信号をすばやく処理するため、遅滞なくアップデートが表示されます。電気サージに対する保護が組み込まれています。つまり、より信頼性が高く、重要な用途では長持ちします。

74HC573ラッチはどのように動作しますか?

74HC573ラッチは、8つのD型透明ラッチを使用してデータフローを制御します。これがどのように機能しますか:

•有効になった場合(G High):出力(Q)は、入力(D)をすぐに直接一致させます。

•無効になった場合(g low):ラッチは最後の入力値を保持し、所定の位置に「ロック」します。

このラッチは、データを安定させるために重要な信号が変更された場合でもデータを保持できます。独立して動作するため、古いデータを保持しながら新しいデータをキャプチャできます。これに慣れていない場合は、各ラッチを、「G.」とラベル付けされたEnable入力と呼ばれる制御信号に応じて、すぐにデータを渡すか、それを保持できる小さなメモリユニットと考えてください。有効な信号が高い(G High)の場合、ラッチは「透明」です。つまり、入力(d)に存在するデータが存在するデータは、オープンゲートのように遅滞なく出力(Q)に直接渡すことができます。ただし、有効な信号が低く(g低)、ゲートが閉じ、ラッチが新しいデータの渡しを停止します。代わりに、ゲートが閉じる前に入力にあった最後のデータをロックして保持し、有効な信号が再び高くなるまでその出力を維持します。入力データが変更されたとしても、有効な信号が低い限り出力は安定したままで、データの整合性を確保し、システムが情報を確実に処理または保存できるようにします。

74HC573ラッチを効果的に使用する方法は?

入力ピンと出力ピンを接続します

まず、入力ピン(D0-D7)をCPUまたはコントローラーの出力ピンにしっかりと接続してください。これらの接続はデータフローが必要なので、短くて高品質のケーブルを使用して、信号損失を防ぎます。次に、出力ピン(Q0-Q7)をセカンダリデバイスに接続します。データは、出力Enable(OE)ピンをアクティブにするまで安定したままで、必要なときにデータを正確に送信できます。

データ送信の制御

CPUは、データを入力(D0-D7)に書き込むことで担当し、データフローを制御するために出力Enable(OE)とLatch Enable(LE)ピンを操作します。これにより、正確なラッチとタイムリーな伝送が保証されます。OEピンは、ラッチされたデータが出力ピンに表示されるかどうかを制御します。それが低い場合、データはQ0-Q7に存在しますが、それが高い場合、出力は高インピーダンス状態に入り、ラッチを効果的に分離します。一方、LE PINは、入力データがラッチされる時期を決定します。入力データは継続的にラッチされ、D0-D7の状態を反映していますが、それが低い場合、ラッチは最後の入力データを保持します。安定した出力を提供します。

複数の74HC573チップをカスケードします

いくつかの周辺機器を含む高度なデータタスクの場合、複数の74HC573チップをカスケードできます。各チップの有効化と制御信号の正確なタイミングは、競合を回避し、シームレスなデータ交換を確保するために必要です。制御信号の効果的な計画は、カスケードチップ全体の信号の整合性を支持します。

信号の品質を確保し、干渉を減らす

抵抗器とコンデンサは、ノイズを除外し、電源ラインを安定させ、データフローを破壊する可能性のある信号反射を最小限に抑えます。CPUおよび周辺機器への74HC573ラッチの緊密な配置により、信号遅延と干渉が最小限に抑えられ、伝送速度と信頼性が向上します。PCB設計で地上飛行機とシールドされた痕跡を使用すると、さらにボルスターが整合性を信号を送り、スムーズで効率的なデータ処理を確保します。

ラッチデータのクリア

新しいデータを採用する前に、74HC573ラッチの現在のデータをクリアします。初期化フェーズ中にリセットルーチンを実装して、データの精度を維持します。慎重に取り扱い、正確な構成、および信号の品質とレイアウトに鋭い注意を払うことで、データ送信とストレージタスクのピークパフォーマンスを達成できます。

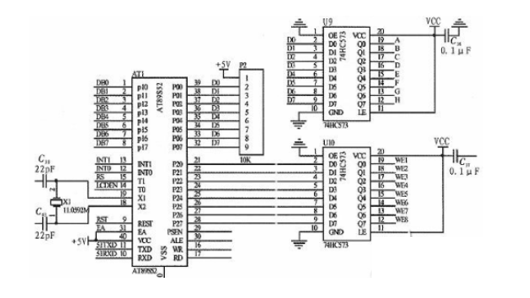

サーキットでの74HC573の適用

74HC245は74HC573の代替ですか?

74HC245は、非同期通信用に設計された3つの状態の出力を備えた人気のある8ビットトランシーバーです。多くの場合、2つのバス間の双方向データフローを管理するために使用されます。デバイスは方向制御を備えているため、データは柔軟にデータを両方向に移動できます。一方、74HC573は、3状態の出力を備えたオクタルD型透明ラッチです。一時的なデータストレージと必要になるまで情報を保持するために使用されます。ラッチ機能は、非同期シグナルを扱う際にデータの安定した流れを提供します。

74HC245は、方向制御を提供することにより、バス間でデータ転送を効率的に管理することに優れています。一方、74HC573は、データをラッチする安定した手段を提供し、システムがその使用を必要とするまでそれを保持します。データストレージに明確に焦点を当てることで、74HC573は、データの連続性が優先事項であるアプリケーションに適しています。74HC245は、その双方向性能力を備えており、動的なデータ処理アプローチを導入します。74HC245は、処理中にデータの整合性を維持する耐久性を提供する74HC573とは異なり、運用ダイナミクスの柔軟性に傾いています。

74HC573を回路設計の74HC245に置き換える場合、それらの違いに注意することが重要です。74HC245の双方向データ制御は、74HC573のいくつかの機能をカバーできます。ただし、74HC245にはラッチング機能がないため、追加のコンポーネントなしではデータを単独で安定させることはできません。これは、74HC573を74HC245に置き換えると、データを一貫して保持する回路の能力に影響を与える可能性があることを意味します。一方、バス間の高速データ交換とスムーズな通信に焦点が当てられている場合、74HC245がより良い選択であり、システムの応答性を高めます。

よくある質問(FAQ)

1。74HC573とは何ですか?

74HC573は、3状態の出力を備えた8ビットDタイプの透明ラッチで、ラッチイネーブル(LE)と出力Enable(OE)入力を備えています。LEが高い場合、入力のデータはラッチに入ります。中間データストレージとステージングを必要とするシナリオで重要な役割を果たし、規制された効率的なデータバスアクティビティを確保します。このコンポーネントは、データをバッファリングしてバスにアドレス指定するために、マイクロコントローラーシステムで一般的に採用されています。

2。74HC574と74HC573の違いは何ですか?

74HC573は、高いLE出力によって活性化されるオクタルD型透明ラッチです。一方、74HC574は、LE出力の正のエッジによって活性化されるオクタルD型フリップフロップです。74HC573は、LEが高く、必要に応じて情報の流れを促進しながら、リアルタイムのデータパッセージを可能にします。74HC574は、LE遷移でデータをキャプチャして保持し、14回のポストサイクルを確保します。この機能は、同期されたデータ転送アプリケーションで有益です。

3. 74HC573の電源電圧範囲はどのくらいですか?

74HC573の典型的な電源電圧範囲は、2.0Vから6.0Vの範囲です。この変動性は実質的な柔軟性を提供し、74HC573を最小限の電源調整の必要性で多様なシステムに統合できるようにします。このような適応性は、さまざまな回路設計にわたって電力効率を最適化する上で有利であることが証明されており、電力に敏感なアプリケーションに適した選択肢となっています。

4。74HC573の機能は何ですか?

74HC573は、デジタル電子回路に8ビットのデータを保存および出力できる3つの状態の出力を備えたオクタル透明ラッチとして機能します。中間データホルダーとしてのその役割は、異なるコンポーネント間のデータフローの管理に優れています。この機能は、データの可用性と遅延管理を正確に制御することを要求するアプリケーションで広く利用されています。このラッチは、データの精度とシステムの安定性を確保するのに役立ちます。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

LL4148スモール信号ダイオードでサーキットを最適化します

09/24/2024で公開されています

TPS54331DRの理解:機能、アプリケーション、セットアップ

09/24/2024で公開されています

ホットポスト

-

回路のGNDとは何ですか?

01/1/1970で公開されています 2933

-

RJ-45コネクタガイド:RJ-45コネクタカラーコード、配線スキーム、R-J45アプリケーション、RJ-45データシート

01/1/1970で公開されています 2489

-

ファイバーコネクタタイプ:SC対LCおよびLC対MTP

01/1/1970で公開されています 2080

-

エレクトロニクスVCC、VDD、VEE、VSS、およびGNDの電源電圧の理解

11/8/0400で公開されています 1878

-

DB9とRS232の比較

01/1/1970で公開されています 1759

-

LR44バッテリーとは何ですか?

そのユビキタスな力は、些細なガジェットから生命を脅かす医療機器まで、私たちの日常生活のあらゆる側面に静かに浸透し、静かな役割を果たします。しかし、このエネルギーを本当に把握し、特にそれを保存して効率的に出力する方法は、簡単な作業ではありません。この背景に反して、この記事は、表面上では重要ではないように見えるかもしれないが、実際の用途、つまりLR44バッテリーでは非常に用途が広いものになる可能性のあるコ...01/1/1970で公開されています 1710

-

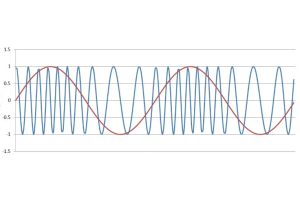

基礎を理解する:インダクタンス抵抗、および副次的

電気工学の複雑なダンスでは、基本的な要素のトリオが中心的な舞台、つまりインダクタンス、抵抗、静電容量です。それぞれが、電子回路の動的なリズムを決定するユニークな特性を備えています。ここでは、これらのコンポーネントの複雑さを解読し、広大な電気オーケストラ内でそれらの明確な役割と実用的な使用を明らかにするための旅に着手します。インダクタンス、その磁束魔法のwizardry;抵抗、電流の流れの不動の門番;電荷のア...01/1/1970で公開されています 1650

-

CR2430バッテリー包括的なガイド:仕様、アプリケーション、およびCR2032バッテリーとの比較

CR2430バッテリーとは何ですか?CR2430バッテリーの利点規範CR2430バッテリーアプリケーションCR2430相当CR2430対CR2032バッテリーCR2430サイズCR2430と同等物を購入するときに何を探すべきかデータシートPDFよくある質問 バッテリーは小さな電子機器の中心です。利用可能な多くのタイプの中で、コイン細胞は、計算機、リモートコントロール、および時計によく見られる重要な役割を果たします。サイズが小さいにもかかわらず、各コ...01/1/1970で公開されています 1539

-

RFとは何ですか?なぜそれを使用するのですか?

無線周波数(RF)テクノロジーは、最新のワイヤレス通信の重要な部分であり、物理的な接続なしで長距離にわたってデータ伝送を可能にします。この記事では、RFの基本を掘り下げ、電磁放射(EMR)がRF通信を可能にする方法を説明します。EMRの原則、RF信号の作成と制御、およびそれらの幅広い用途を探ります。この記事では、RFテクノロジーの歴史的なマイルストーン、関係する技術的課題、および信頼できるRFコミュニケーションを確...01/1/1970で公開されています 1533

-

CR2450対CR2032:代わりにバッテリーを使用できますか?

リチウムマンガンバッテリーには、他のリチウム電池といくつかの類似点があります。高エネルギー密度と長いサービス寿命は、彼らが共通している特性です。この種のバッテリーは、独自の安全性のために多くの消費者の信頼と好意を獲得しています。高価なハイテクガジェット?私たちの家に小さな電化製品?周りを見回すと、どこにでも表示されます。これらの多くのリチウムマンガンのバッテリーの中で、CR2450バッテリーとCR2032バッ...01/1/1970で公開されています 1503