ペースの速いデジタル時代におけるフラッシュADCの可能性を解き放つ

デジタルテクノロジーの急速な成長により、アナログとデジタルの世界を接続するのに最適な効率的なアナログ間コンバーター(ADC)を開発することが重要になりました。この記事では、Flash ADCがどのように機能するか、コンポーネントがどのように動作するか、および他のADCタイプと比較する方法について説明します。また、最新のエレクトロニクスにおけるそれらの重要性を強調し、エンコーダでXorゲートを使用したり、エンコード速度を向上させるダイオードマトリックスなどのADC設計の改善に注目しています。カタログ

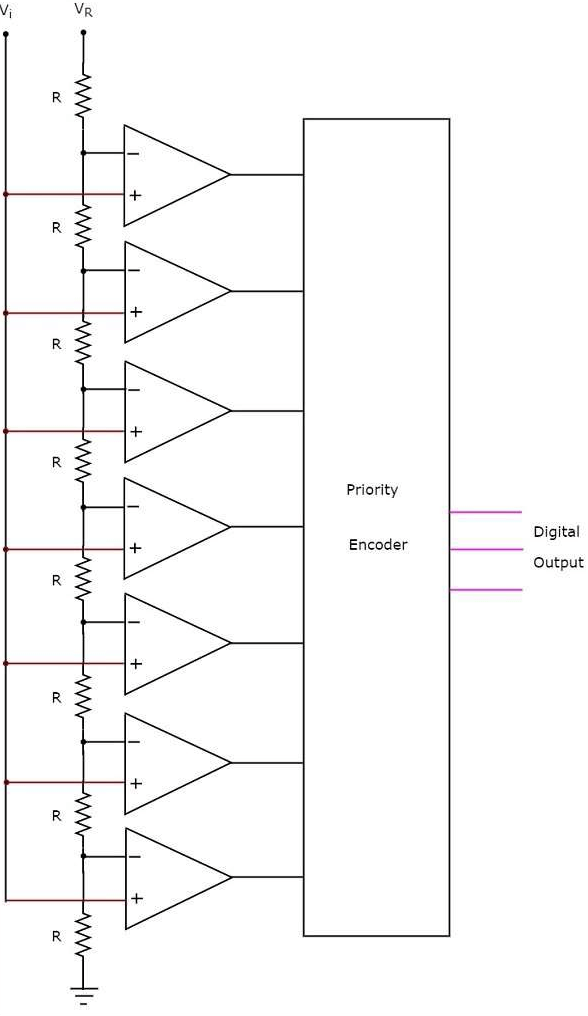

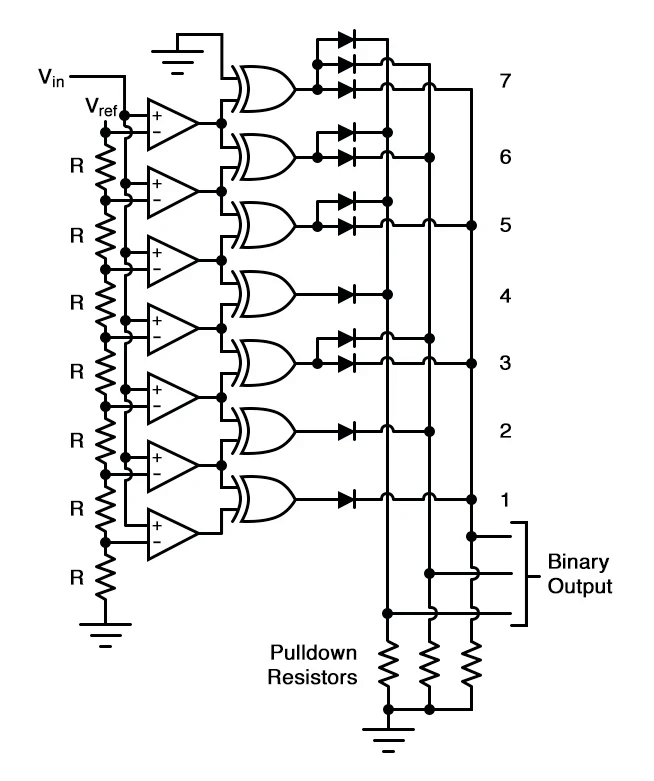

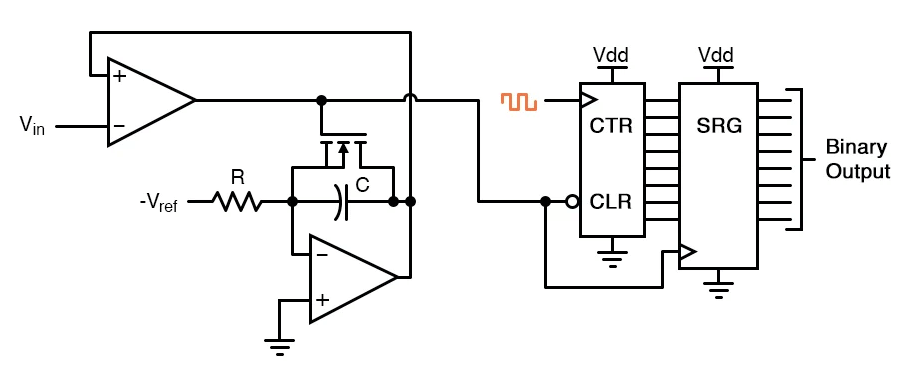

図1:フラッシュADC回路

Flash ADCについて最初に何を知っておくべきですか?

フラッシュADC、または平行(アナログ間コンバーター)は、最も単純なタイプのアナログからデジタルコンバーターです。コンパレータの行を使用して、着信アナログ信号を異なる基準電圧と比較します。これらのコンパレータからの出力は優先エンコーダーに移動し、入力信号のデジタルバイナリバージョンを提供します。この簡単なセットアップにより、ADCがどのように機能するかを簡単に理解し、直接比較方法により迅速な変換を可能にします。

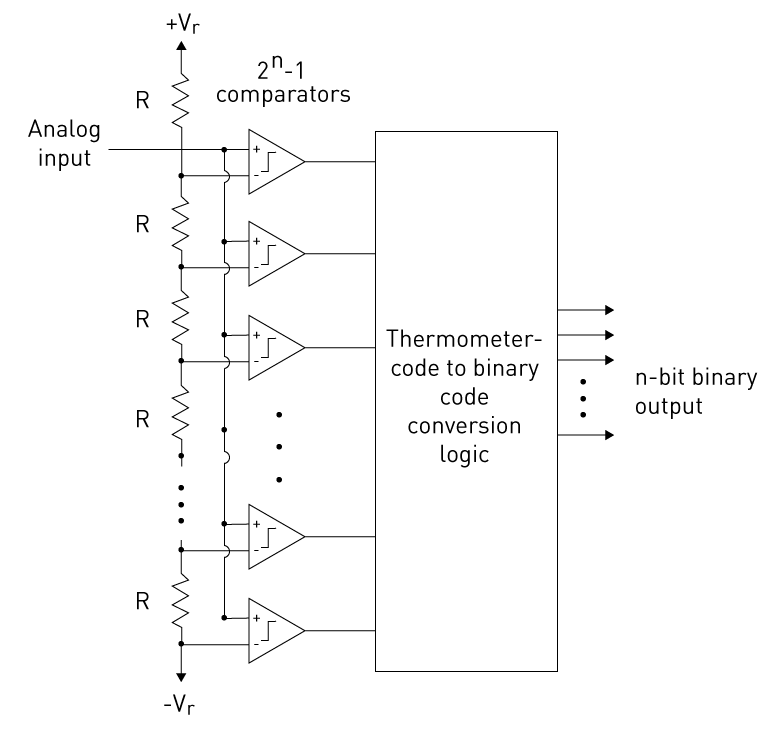

NビットフラッシュADCは、N-1コンパレータ、2セットのマッチング抵抗、および優先エンコーダーで構成されています。この概念を示す図を以下に示します。

図2:フラッシュADC構造

フラッシュADCの主要コンポーネント

抵抗電圧分割回路

抵抗電圧分割回路は、フラッシュADC(アナログからデジタルコンバーター)の基本部分です。これにより、高入力電圧を単純な方法で使用可能なレベルに低下させるのに役立ちます。この回路は一連の抵抗を使用して電圧を分割するため、抵抗値を調整することで出力電圧を簡単に制御できます。Kirchhoffの電圧則を使用すると、出力電圧を正確に計算できます。これは、正確な基準電圧が必要なアプリケーションにとって重要です。

たとえば、直列に接続されている2つの抵抗器、R1とR2の分裂者を検討してください。ジャンクションの出力電圧(Vout)は、式Vout =(R2×Vin) /(R1 + R2)で与えられます。この方程式は、入力電圧(VIN)と抵抗の関係を示しており、電圧分割器が電圧出力をどのように変化させるかを示しています。このメカニズムは、電子システムのさまざまな部分に安定した正確な電圧を作成するために重要であり、抵抗電圧分割器を高度な電子設計の主要部分にします。

コンパレータ

フラッシュADCのコンパレータは、アナログ信号をデジタル形式に変更するのに役立つ主要部分です。単純なアンプのように機能し、入力電圧を基準電圧と比較し、2つの差を示すバイナリ出力を与えます。このバイナリ信号は、入力電圧が基準電圧よりも高いか低いかを示すため、デジタル化に重要です。

コンパレータは、入力電圧を正の入力(v+)で、およびネガティブ入力(v-)で参照電圧を取得します。出力(VOUT)は、V+がV-よりも大きい場合は高(ロジックレベル '1')になり、そうでない場合は低(ロジックレベル '0')になります。ADCには、アナログ信号のデジタルバージョンが作成されるため、このアクションが必要です。バイナリ状態を正しく識別することにより、コンパレータはADCが電子デバイスで高品質のデジタル結果に適したさまざまなアナログ信号を正確に処理するのを支援します。

優先エンコーダー

優先度エンコーダは、アナログ間変換プロセスをより正確で信頼性を高めることにより、フラッシュADCの動作を改善します。通常のエンコーダーとは異なり、複数の入力が混乱することなく同時に高い状況を処理します。これは、入力をランク付けする優先システムを使用してこれを行い、最優先信号が常に出力に表示されることを確認します。

たとえば、1からnの入力番号を持つ優先エンコーダーが同時にN-1、4、2などの複数の高入力を検出すると、最高優先入力のバイナリコードが出力されます。場合。この優先順位付けにより、ADCの出力が正確になります。これは、アナログ信号の正確なデジタルバージョンを必要とするタスクにとって重要です。優先エンコーダーは、入力競合を効果的に処理し、エラーを防ぎ、ADCがより効果的かつ信頼できる動作を支援することにより、デバイスの全体的なパフォーマンスを大幅に改善します。

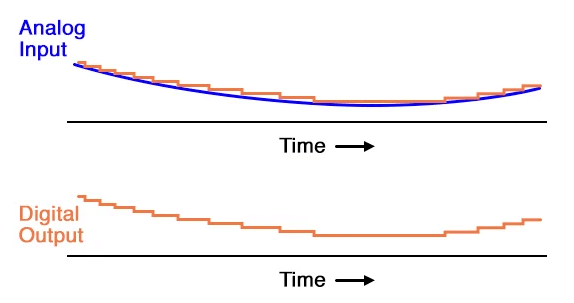

フラッシュADCの運用ダイナミクス

フラッシュADCは、アナログ入力信号を対応するデジタル出力にリアルタイムで変換することにより動作します。このプロセスには、それぞれ異なる参照電圧レベルに調整された多重コンパレータ段階を介した入力信号の迅速な評価が含まれます。結果は、フラッシュADC設計の固有の効率と速度を紹介するアナログ入力に直接対応する即時のデジタル出力となります。

図3:フラッシュADCと出力

並列比較

Flash Analog-to-Digitalコンバーター(ADC)は、アナログ信号をデジタル形式に迅速に変換する能力の中心であるParallel比較と呼ばれる手法を使用して動作します。この方法は、写真の迅速な露出と同様に、フラッシュADCの「フラッシュ」を反映しています。このメカニズムの中心にあるのは、抵抗のはしごから導出された複数の基準電圧に対する入力アナログ電圧の同時評価です。このコンポーネントは、ADC内に参照ベンチマークを確立するための一部です。

配列内の各コンパレータは、特定の役割を実行します。着信電圧を指定された参照電圧と比較します。これらの比較を実行すると、フラッシュADCが高速で動作することができます。これは、他のADCタイプで見られる遅い順次比較とはまったく対照的です。これらの同時比較の結果は温度計コードであり、これは連続 '1に続く' 0が続く一連のシーケンスです。たとえば、5つのコンパレーターフラッシュADCでは、3つのコンパレータの参照電圧を超える入力電圧が11100の温度計コードになります。このコード形式は、アナログ入力をデジタル信号に直接変換し、さらなるデジタル処理のための入力電圧。

エンコーディングプロセス

フラッシュADCで温度計コードを生成した後、エンコードフェーズが開始されます。この手順は、温度計コードを標準のバイナリ形式に変換するため重要です。これにより、必要な出力ラインの数が減り、デジタルデータの管理と処理が容易になり、効率が向上します。

優先エンコーディングは、このタスクに一般的に使用されます。温度計コードで最高の「1」の位置を見つけ、その位置をバイナリ数に変えることで機能します。たとえば、コード11100では、最高の「1」が3番目の位置にあり、3ビットADCのバイナリ番号011に変換されます。この方法により、最も重要な入力が正確に表され、入力電圧のコンパクトなデジタル形式を提供することが保証されます。灰色のコードなどの他のエンコーディング方法を使用して、信号の転送と処理中のエラーを減らすために使用される場合があります。エンコードは、フラッシュADCの高速機能に一致するために迅速に進む必要があります。これを達成するために、Flash ADCは効率的な動作のために設計された特別なエンコード回路を使用します。これらの回路により、高速かつ正確なエンコードが可能になり、デバイスの迅速な応答と高いデータスループットが維持されます。

フラッシュADCの動作

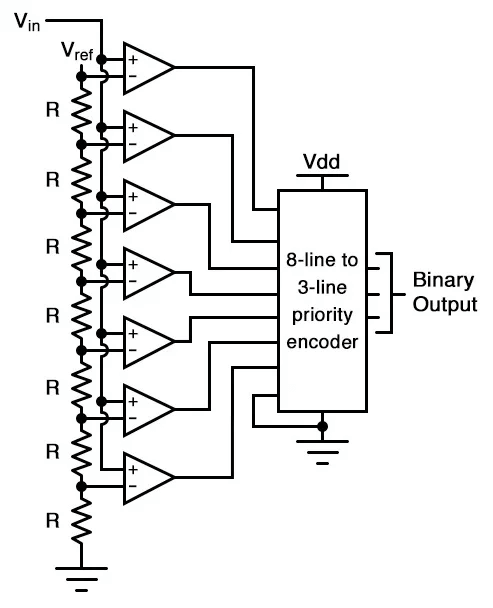

図4:フラッシュADC

Flash Analog-to-Digitalコンバーター(ADC)は、アナログ信号をデジタル形式にすばやく変換するため、高速デジタルアプリケーションで最適です。アナログ入力を迅速にデジタル出力に変換するために、フラッシュADCは、高速コンパレータの複雑なシステムで構築されます。このネットワークは、抵抗電圧分割を使用して、コンパレータ全体に基準電圧を分布させます。

フラッシュADCでは、各コンパレータは入力電圧を特定の参照レベルと比較します。各コンパレータの参照レベルは、シーケンス内の位置によって設定されます。たとえば、NビットフラッシュADCには、2^n -1のコンパレータがあります。各コンパレータの参照電圧は、前のコンパレータよりも少し高くなっています。このセットアップにより、「温度計コード」出力パターンが作成されます。このパターンでは、バイナリの出力パターンは、アナログ入力電圧がコンパレータの基準電圧を下回るポイントでゼロに変化します。このパターンは、温度計の水銀がどのように上昇するかに似ており、停止するポイントに達するまでより高い値を継続的にマークします。

フラッシュADCのコンパレータは、高周波信号を処理するように設計されています。通常、帯域幅とゲインのバランスをとるために、広帯域の低ゲインの運用段階を持っています。パフォーマンスを維持し、問題を防ぐために、より高い周波数で低ゲインが必要です。また、各コンパレータは、実際の信号の一部ではないマイナー電圧の変化による誤った測定値を回避するために、LSBよりも小さい非常に小さな電圧オフセットで設計されています。コンパレータが信頼できる出力を提供するために、フラッシュADCは各出力段階で再生ラッチを使用します。これらのラッチは、肯定的なフィードバックを使用して、出力状態を1または0にロックします。不明確な出力を排除するには、特に高速データ変換でこの明示的な意思決定が必要です。

フラッシュADCの最適化とは、コンパレータのゲインを調整し、電圧オフセットを削減し、ラッチフィードバックを改善することにより、設計を改良することを意味します。これらの改善により、Flash ADCは、精度、速度、および信頼性を高めることにより、デジタルエレクトロニクスにさらに影響を与えます。これらの機能強化により、Flash ADCはより高いパフォーマンス基準を満たし、迅速かつ正確なアナログからデジタルへの変換を必要とする高度なデジタルアプリケーションを効果的に提供します。

3ビットフラッシュADC回路

図5:3ビットフラッシュADC回路

3ビットフラッシュADC(アナログからデジタルコンバーター)回路は、アナログ信号をデジタルの信号に変換するために使用される電子システムです。ADCの動作に必要なVREFとして知られる正確で安定した基準電圧があると想像してください。このVREFは、電圧が一定かつ正確なままであることを保証する高精度電圧レギュレータによって供給されます。この回路には、いくつかのコンパレータがあります。各コンパレータは、入力アナログ電圧を特定の基準電圧レベルと比較するデバイスです。入力電圧が特定のコンパレータの基準電圧よりも高くなると、そのコンパレータの出力は高状態に切り替わります。つまり、アクティブになります。

コンパレータは順番に配置されます。したがって、アナログ入力電圧が増加すると、より多くのコンパレータが次々にアクティブになります。この一連のアクティブ化は、入力電圧のレベルを示します。これらすべてのコンパレータからの出力は、優先エンコーダーに送信されます。優先度エンコーダーの役割は、アクティブなコンパレータ出力を調べてバイナリ番号に変換することです。このバイナリ番号は、現在アクティブな最高のコンパレータを表し、アナログ入力電圧のデジタル表現を効果的に提供します。そのため、3ビットフラッシュADC回路は、安定した基準電圧を使用して、入力電圧と比較します。入力電圧が上昇すると、より多くのコンパレータが順番に高い状態に切り替わります。これらのアクティブな状態は、優先度エンコーダーによってバイナリ番号にエンコードされ、アナログ入力電圧に対応するデジタル出力を与えます。このプロセスにより、アナログ信号をデジタルフォームに迅速かつ効果的に変換することができます。

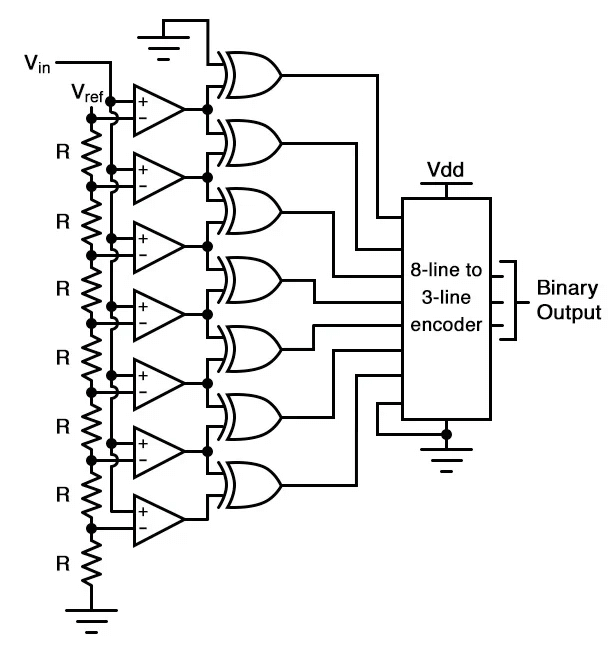

Flash ADCシステムのエンコーダー設計を簡素化します

図6:フラッシュADC

優先度エンコーダーはいくつかの入力を調べ、アクティブな最高優先順位の入力を選択します。この選択プロセスは、システムがどの信号を処理するかを理解するのに役立ちます。ただし、一部のアプリケーションでは、標準の優先度エンコーダーのすべての機能を必要としない場合があります。これらの状況では、フラッシュADCのコンパレータ出力の自然特性を利用できます。比較器は、2つの電圧を比較し、より高い信号を出力するデバイスです。フラッシュADCでは、これらのコンパレータ出力は、多くの場合、順次順番に低くなります。これは、出力が自然に最も低いものから最高に順序付けられることを意味します。

この自然な順序を使用することにより、設計を簡素化できます。複雑な優先度エンコーダーを使用する代わりに、一連の排他的(XOR)ゲートを使用できます。Xor Gatesは、入力が異なる場合にのみ真であることを出力する基本的なロジックゲートです。これらのXORゲートを慎重に配置することにより、優先度エンコーダーによく似ているが、複雑さが少ない最高のアクティブ入力を効果的に選択するエンコードメカニズムを作成できます。

このよりシンプルなエンコーディングメソッドは、コンパレータ出力のシーケンシャルな「高」状態飽和を活用するため、うまく機能します。本質的に、システムは自然にそれ自体をソートし、Xorゲートはこの並べ替えられた状態を読むのに役立ちます。これにより、ADCシステムの全体的な複雑さが減少し、迅速なパフォーマンスを維持しながら、構築が容易で安価になります。この方法でXor Gatesを使用すると、優先度エンコーダーと同じ効果を達成できますが、パーツが少なく、複雑な設計作業が少なくなります。

ダイオードマトリックスを使用したエンコーダー回路の構築

エンコーダー回路を構築する効率的で簡単な方法の1つは、ダイオードのマトリックスを使用することです。ダイオードは電子コンポーネントであり、電流が反対方向にブロックしながら一方向に流れるようにします。これらのダイオードをマトリックスに配置することにより、異なる入力信号を解釈して対応するデジタルコードを生成するシステムを作成できます。この方法は最小限で効果的であり、コンバーター回路の構築に人気のある選択肢となっています。

ダイオードマトリックスを使用するシンプルさは、複雑なコンポーネントや高価なコンポーネントを必要としないことを意味します。代わりに、基本的な電子部品を使用して、目的の機能を実現できます。この実用的なアプローチは、電子機器について学んでいる人や、リソースが限られているプロジェクトに取り組んでいる人にとって有益です。

フラッシュADCでは、速度が重要です。エンコーダ回路は、アナログ信号をデジタル形式に迅速かつ正確に変換する必要があります。ダイオードマトリックスは、高速で動作できるため、このタスクに適しています。ADCシステムの全体的な効率を保証します。ダイオードマトリックスを使用したエンコーダー回路の構築は、実用的で効果的な方法です。基本的なコンポーネントを使用してADCシステムの組み立てが可能になり、多くの電子愛好家や専門家にとってアクセス可能なオプションになります。

図7:ダイオードマトリックスを備えたフラッシュADC

フラッシュADCと他のADC

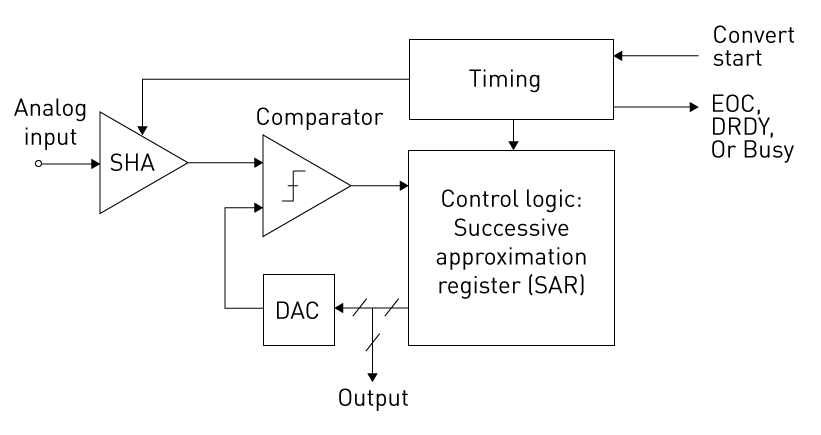

図8:N-Bit Flash ADC

図9:SAR構造

Flash vs. SAR ADCS

Flash ADCとSAR ADCは、速度、電力効率、コストの点で大きく異なります。SAR ADCは、最も重要なビット(MSB)から最も重要なビット(LSB)まで、各ビットを1つずつ決定することで機能します。彼らは、DAC出力と継続的に比較する高精度コンパレータを使用して、プロセスを徐々に遅くし、速度を毎秒数百万サンプル(MSP)に制限します。一方、Flash ADCは、アナログ入力全体を1つのクイックステップでデジタル信号に変換します。これにより、彼らは速度が優れており、多くの場合、ギガサンプルあたりの速度(GSP)範囲で速度を達成します。

たとえば、MAX1132と同様に、SAR ADCは最大16ビットまでの解像度を提供できます。それに比べて、フラッシュADCは通常、約8ビットの解像度を提供します。ただし、この速度にはトレードオフが付いています。MAX1106などの8ビットSAR ADCは、3.3ボルトで電流の約100マイクロアンペア(µA)のみを使用し、毎秒25キロサンプル(KSP)の速度で動作します。対照的に、Flash ADC MAX104は5.25ワットを消費します。これは、消費電力が16,000倍増加します。

さらに、SAR ADCははるかに費用対効果が高く、より小さなパッケージに入っています。それらは生産するのがよりシンプルで安価であり、多くのアプリケーションにとってより良い選択肢となっています。フラッシュADCは、高電力のニーズにより、熱散逸を管理し、信号の整合性を維持するために、より大きなパッケージが必要です。たとえば、MAX104パッケージはMAX1106のパッケージよりも50倍以上大きくなっています。サイズと電力効率のこの違いにより、SAR ADCはコストや電力などの状況で好ましい選択になります。

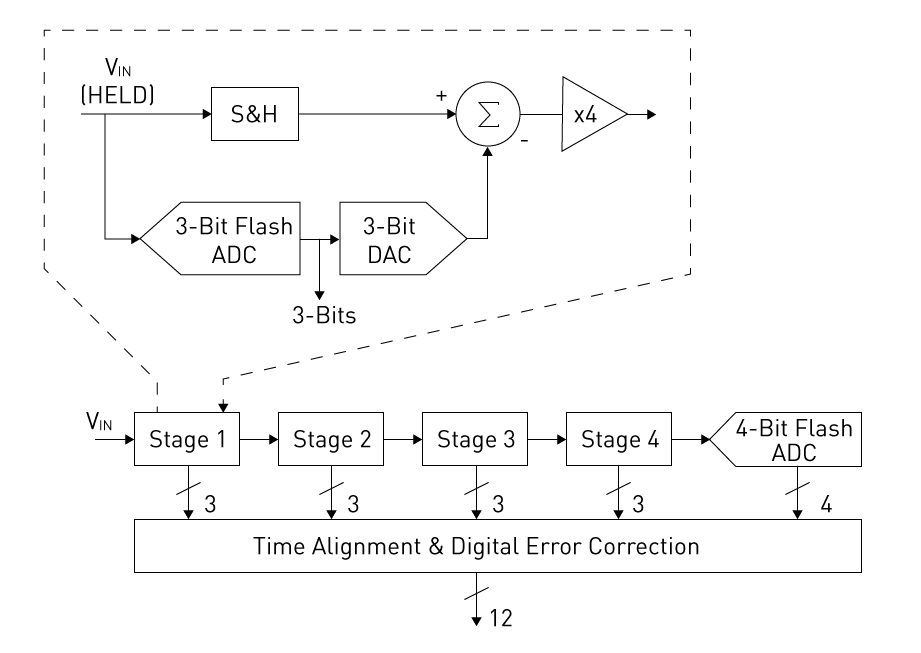

Flash vs. Pipelined ADCS

図10:12ビットパイプライン型ADC

それぞれに独自のデザインと特性があり、速度、消費電力、解像度に基づいてさまざまなニーズに応えています。Pipelined ADCは、並列処理構造を使用して動作します。これは、異なる段階で複数のサンプルからのビットを同時に処理できることを意味します。各ステージは、サンプルの一部を次の段階に渡す前に処理し、より連続的なデータの流れを可能にします。この設計は、全体的な処理速度を向上させることを目的としています。ただし、この並列処理にはコストがかかります。PipelinedADCは、より多くのパワーを消費し、各段階がタスクを完了するのに時間がかかるため、ある程度の遅延を導入する傾向があります。たとえば、Pipelined ADCの一種であるMAX1449は、8〜14ビットの範囲の解像度で最大1億サンプル(MSP)の速度を達成できます。これにより、パイプラインのADCは、中程度から高速から解像度を必要とするアプリケーションに適しています。

一方、Flash ADCは、単純なコンパレータを使用してよりシンプルなアプローチを使用します。アナログ信号をデジタル信号にほぼ瞬時に変換することができ、パイプラインのADCよりもはるかに高速になります。フラッシュADCは非常に高速、多くの場合数百MSPを達成できますが、通常、最大10ビットの低い解像度を提供します。それらのシンプルさと速度により、デジタルオシロスコープや高周波通信システムなどのアプリケーションに最適です。

その違いにもかかわらず、フラッシュADCとパイプラインのADCは、ハイブリッド構造で互いに補完することができます。このような構成では、Flash ADCは他のシステムに統合され、速度を高めながら、望ましい解像度と精度を維持します。この相乗効果により、パフォーマンスが向上し、各タイプの強度を活用して特定のアプリケーション要件を満たす方法を示します。Pipelined ADCは、中程度の速度でより高い解像度のために設計されており、より複雑な処理が含まれますが、Flash ADCは、よりシンプルなデザインで低い解像度で非常に高速を達成することに優れています。それらの明確な機能とアプリケーションを理解することは、特定のタスクに対して適切なADCを選択するのに役立ちます。

Flash vs. ADCの統合

図11:ADCの統合

フラッシュADCは、アナログ信号をデジタルフォームに変換するのが非常に高速であるため、リアルタイム処理が必要なタスクに最適です。これらのタスクには、デジタルオシロスコープ、ビデオ信号処理、レーダーシステムが含まれます。ただし、フラッシュADCの解像度は低く、多くの場合6ビットから8ビットの範囲ですが、より高い解像度はより高いコストで複雑になります。高速のため、Flash ADCはより多くの電力を消費します。これは、電力保存が重要なアプリケーションの欠点となる可能性があります。また、多くのコンパレータと抵抗器を含む複雑な構造により、それらはより高価になります。

一方、ADCの統合は遅く、1秒あたり数百のサンプルで動作します。この遅い速度は、リアルタイムの処理には適していないことを意味します。代わりに、シグナルがゆっくりと変化するアプリケーションに最適です。または、産業設定でのDC信号を監視するなど、時間の経過とともに高い精度を必要とするアプリケーションに最適です。ADCを統合すると、通常は16ビット以上の非常に高解像度が得られ、信号レベルの小さな変化を非常に正確に検出できます。また、電力はほとんど消費されておらず、バッテリー操作や低電力のアプリケーションに最適です。さらに、ADCの統合は一般に、Flash ADCよりも手頃な価格であるため、その単純な構造にはコンポーネントが少ないためです。

フラッシュADCは、より高い消費電力とコストにもかかわらず、リアルタイムのデータ変換が必要な高速アプリケーションに最適です。一方、ADCの統合は、電力効率と費用対効果が重要な高解像度の低速アプリケーションに最適です。

Flash vs. Sigma-Delta ADCS

図12:Sigma-Delta ADCS

Sigma-Delta ADCは、高解像度で知られています。それらは、精度が速度よりも重要である状況で最もよく機能するように設計されています。これらのADCは通常、低帯域幅のアプリケーションに使用され、通常は1 MHz未満です。オーバーサンプリングと呼ばれるプロセスを使用することにより、12〜24ビットの範囲の非常に高い解像度を達成できます。このプロセスでは、多くのサンプルを採取し、ノイズを減らすフィルタリング技術を使用して、アナログ信号の非常に正確なデジタル表現を生成します。ただし、Sigma-Delta ADCには欠点があります。比較的遅いです。これにより、特に多くの信号を迅速に処理する必要があるマルチチャネルセットアップでは、高速データ変換が必要なアプリケーションには適していません。この制限にもかかわらず、連続時間Sigma-Delta ADCには継続的な開発があります。これらの進歩は、速度を改善することを目的としており、潜在的に実行可能な競合他社に、データレートが低いが解像度が高いシナリオでADCをフラッシュするようにします。

一方、フラッシュADCは速度のために構築されます。アナログ信号を非常に高いレートでデジタルに変換することができ、高周波環境に最適です。ただし、通常、Sigma-Delta ADCと比較して解像度が低くなります。Sigma-Delta ADCの制限速度を克服するために、エンジニアはSigma-Deltaシステム内にFlash ADCモジュールを統合する方法を模索しています。このハイブリッドアプローチは、高速のフラッシュADCとSigma-Delta ADCの高解像度を組み合わせることを目的としており、その結果、全体的なパフォーマンスが向上するために両方のテクノロジーの強度を活用するシステムが生まれます。

フラッシュADCの利点と短所

|

側面 |

詳細 |

|

スピード |

フラッシュADCは高速で知られています パフォーマンス。それらは、での複数の参照と入力電圧を比較します 同時に、他のADCで使用される繰り返しの手順をスキップします。これにより、フラッシュが可能になります Millisecondsで出力を生成するADCは、即時データに適しています 処理ニーズ。 |

|

シンプルさ |

フラッシュADCは操作が簡単です。彼らは持っている 並列比較とエンコーディングの2つの段階のみ。このシンプルさはそれらを作ります 理解して運用しやすく、デザインの複雑さと生産を減らす 費用。ただし、解像度が増加するにつれて、より多くのコンパレータが必要です。 複雑な設計と電力管理。 |

|

スケーラビリティと消費電力 |

Flash ADCはうまくスケーリングしません。の数 比較者は、より高い解像度で指数関数的に増加し、 より複雑で、より多くのパワーを必要とするデザイン。この高電力消費はです 熱の管理があるポータブルデバイスと環境に問題があります 必須。 |

|

より高い解像度のための複雑さ |

より高い解像度では、フラッシュADCは非常になります 複雑な。より多くのビットは、より多くのコンパレータとより複雑な抵抗器を意味します はしご、電力管理とレイアウトをより挑戦的にします。この複雑さ 効率、精度、直線性を低下させることができ、正確に必要です キャリブレーション、複雑さとコストの両方を増加させます。より多くのコンポーネントも意味します より多くのチップ領域。これは、スペース制限アプリケーションには理想的ではありません。のために 高解像度のニーズ、連続した近似のような他のADCテクノロジー または、Sigma-Deltaコンバーターは、多くの場合、より費用対効果が高くスケーラブルです。 |

フラッシュADCのアプリケーション

通信システム:Flash ADCは、光ファイバーや衛星通信などの高速ネットワークで機能を提供します。アナログ信号をデジタルフォームに効率的に変換し、長距離にわたって迅速な処理と送信を可能にします。この迅速な変換は、リアルタイムブロードキャストや高頻度取引などのアプリケーションに適したコミュニケーションの品質を維持するのに役立ちます。

医療イメージング:MRIやCTスキャナーなどの医療画像技術では、フラッシュADCも必要です。これらのADCは、ボディによって生成されたアナログ信号をデジタルデータに迅速に変換し、リアルタイムで高解像度画像を作成できるようにします。この迅速かつ正確なデータ変換は、特に緊急の状況での病状の診断と治療に最適です。

電子戦:電子戦の分野では、信号インテリジェンスと電子対策にフラッシュADCが必要です。これらのコンバーターは、複雑なアナログ信号を迅速にデジタル形式に変換し、軍隊が脅威をリアルタイムで特定して打ち消すことができます。この機能は、軍事部隊の戦略的および運用上の応答性を高めます。

デジタルオシロスコープ:電気信号の波形を正確に観察する目的で、デジタルオシロスコープにはフラッシュADCが必要です。これらのADCは、高周波アナログ信号をほぼ即座にデジタル形式に変換します。この迅速な変換は、オシロスコープのデジタルディスプレイがアナログ信号の正確なレプリカであることを保証するため、重要です。これにより、波形の正確な分析と測定に役立ち、フラッシュADCがリアルタイム信号処理に不可欠になります。

レーダーシステム:レーダーテクノロジーは、フラッシュADCに大きく依存しています。レーダーシステムは、これらのコンバーターに依存して、オブジェクトからバウンスするアナログ信号をデジタルデータにすばやく変更します。フラッシュADCは、電子戦争信号インテリジェンスと電子対策において主要な役割を果たします。レーダーシステムには、高精度、防衛操作、監視操作の必要性でオブジェクトを検出および監視する能力が必要です。Flash ADCは、信号をすばやく変換することにより、この機能を提供します。

高速データ収集:Flash ADCは、科学的研究、産業監視、自動テストなど、高速データ収集を必要とする分野で基本的です。これらのコンバーターは、重要な情報を失うことなく、迅速に変化する信号をキャプチャするように設計されています。この高速データ収集は、信号の整合性が重要なアプリケーションでの正確な分析と監視に必要です。

結論

フラッシュADCは、アナログからデジタルへの変換技術の速度のピークを、高速な信号処理を可能にするシンプルで強力なデザインを備えています。この記事では、アナログからデジタルへの迅速な変換が必要な高速でリアルタイムのアプリケーションでの異なる役割を示しています。Flash ADCは操作が簡単ですが、解像度を拡大する上で課題に直面しているため、より複雑な設計とより高い出力が必要です。速度と電力効率と設計の複雑さのトレードオフのこのバランスは、ADCテクノロジーで重要です。より速く、より効率的な電子機器の必要性が高まるにつれて、Flash ADCは、産業技術と消費者技術の両方のニーズを満たすために、デジタルエレクトロニクス、バランス、解像度、電力効率の将来において大きな役割を果たします。

よくある質問[FAQ]

1.フラッシュADCがより速いのはなぜですか?

平行ADCとも呼ばれるフラッシュADCは、入力信号のすべてのビットを同時に処理するため、他のタイプのADCよりも高速です。この並列処理は、入力電圧が特定の基準レベルを上回っているか下にあるかをチェックする一連のコンパレータを使用することによって達成されます。一度にすべての比較を実行し、デジタル値を直接出力するため、フラッシュADCは他のADCタイプで見つかった連続的な近似または反復変換プロセスの必要性を排除します。この設計により、ほぼ瞬間的な変換が可能になり、Flash ADCSが利用可能になります。

2. 2ビットフラッシュADCとは何ですか?

2ビットフラッシュADCは、アナログからデジタルへのアナログからデジタルへのコンバーターの一種であり、アナログ入力信号を4つの可能なデジタル出力(00、01、10、または11)のいずれかに定量化します。3つのコンパレータを使用し、それぞれ入力信号を異なる基準電圧に比較します。これらのコンパレータの出力は、2ビットデジタル値にデコードされます。このADCは、4つのレベルの解像度でアナログ入力を表すことができます。

3. 3ビットフラッシュADCとは何ですか?

3ビットフラッシュADCは、さらに細かい解像度を提供することにより、2ビットバージョンに拡張されます。アナログ入力を8つの可能なデジタル出力のいずれかに変換します(000から111の範囲)。このタイプのADCは7つのコンパレータを使用し、それぞれが異なる基準電圧に設定されています。コンパレータは、入力電圧がそれぞれの参照よりも高いか低いかどうかを同時に評価し、結果は3ビットデジタルコードに変換され、8つの異なるレベルでアナログ入力の表現が可能になります。

4.フラッシュADCはどこで使用されますか?

迅速なデータ変換と高速を必要とするアプリケーションは、フラッシュADCを使用する主なものです。一般的なユースケースには、デジタルビデオブロードキャスト、レーダーシステム、高周波信号処理が含まれます。アナログ信号からデジタル形式へのほぼ吸い込んだ変換のために、応答時間が非常に重要な設定に最適です。

5.アナログ信号は、フラッシュタイプADCを使用してデジタルにどのように変換されますか?

フラッシュADCでは、アナログ入力信号が一連のコンパレータに供給されます。各コンパレータには、入力電圧範囲を等しいセグメントに分割する参照電圧があります。すべてのコンパレータは同時に動作し、それぞれが参照電圧を超えて「0」を超えると、それぞれが「1」のバイナリ出力を提供します。これらのバイナリ出力は、ロジック回路で結合され、コンパレータ出力をアナログ入力に相当するデジタルを表すバイナリ数に変換します。

6.フラッシュADCは何ビットですか?

フラッシュADCのビット数は、その解像度、つまり、アナログ入力範囲をどの程度細かく分割し、それをデジタル出力として表すことができるかを定義します。フラッシュADCは、特定のアプリケーションと必要な精度に応じて、一般に2ビットから10ビット以上の範囲の解像度が大きく異なる場合があります。

7.フラッシュADCの速度はどのくらいですか?

フラッシュADCの速度は、主にそのコンパレータがどれだけ速く沈降できるかによって決定され、そのロジック回路は出力をエンコードできます。通常、Flash ADCは、ナノ秒の順序で変換時間を達成できます。たとえば、高速フラッシュADCは、毎秒500メガサンプル(MSP)から数秒あたりの数ギガサプル(GSP)以上の範囲の速度を提供する可能性があり、他のADCタイプと比較して非常に速くなります。リアルタイム処理と低レイテンシが必要なアプリケーションは、このパフォーマンスに依存します。