S-Rラッチのパワーを理解する:現代のエレクトロニクスへのゲートウェイ

ラッチは、1つの情報を保存し、新しい入力信号を取得するまでその値を保持するシンプルなデジタルデバイスです。これらは、バイナリデータを一時的に保持するためにデジタルシステムで使用されます。ラッチは、さまざまな種類の基本的なロジックゲートを使用して作成できます。この記事では、S-Rラッチの設計、機能、バリエーション、および使用について説明し、現代の電子機器におけるその最良の役割と、実際の回路とデジタルロジックシミュレーションでの使用を強調しています。

カタログ

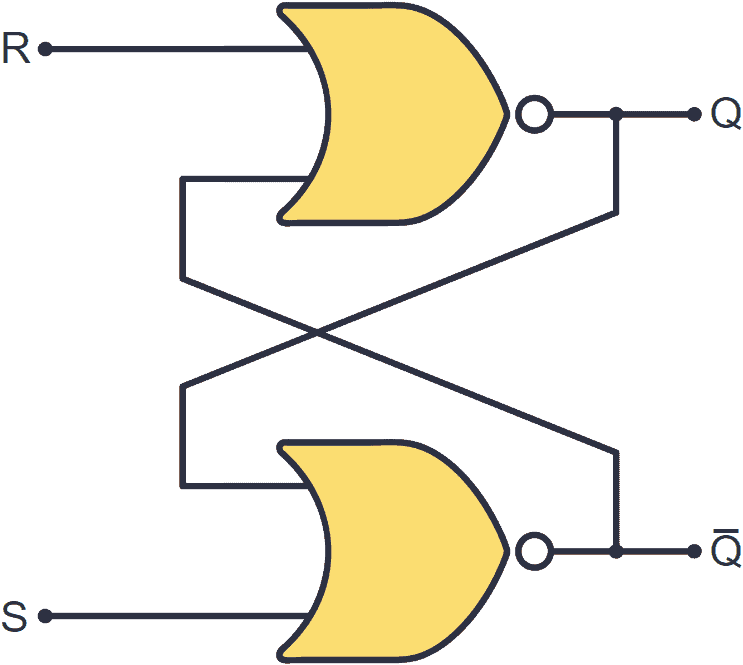

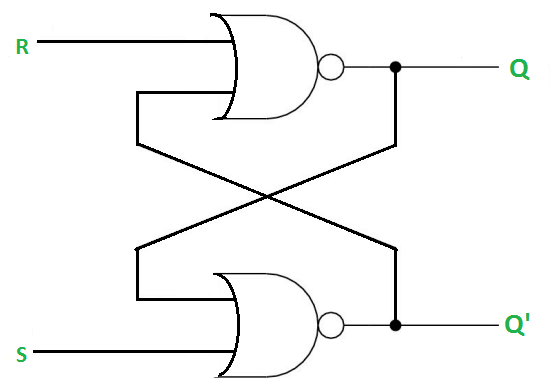

図1:S-Rラッチ回路図

S-Rラッチの構造

Digital Electronicsの礎石であるS-R(Set-Reset)ラッチは、双安定マルチバイブレーターです。外部入力なしでは、2つの異なる安定した状態のいずれかを無期限に維持することができます。この機能により、SRは、さまざまな電子デバイスにわたるメモリストレージおよびスイッチング操作のメインコンポーネントとなります。

構造的には、SRラッチは、フィードバックループ設計に配置された2つの相互接続されたゲートで構成されています。この特定の配置は、双安定性の前提条件を提供するため、重要です。それぞれのGateの出力は、他の出力に直接接続され、ラッチの動作を支えるフィードバックの連続ループを作成します。

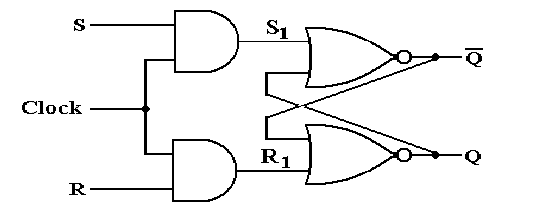

図2:S-Rラッチとクロック信号(CLK)

基本設計を拡大すると、ゲートSRラッチは、追加の入力:クロック信号(CLK)を導入します。この拡張機能には、制御層をもたらすクロック入力が組み込まれており、ラッチ操作を同期を必要とするシステムに統合します。この同期は、ラッチが「ゲート」という用語で適切に説明される状態を変更できる正確な瞬間を決定することを義務付けました。クロック信号を含めることにより、ラッチの出力状態の変化は、通常、CLK信号の上昇または下向きのエッジでアクティブクロックフェーズでのみ発生することが保証されます。

CLK入力の導入は、基本的なSRラッチのプロパティを保持するだけでなく、その動作をより大きなデジタルシステムの時間的ダイナミクスに合わせます。データの整合性を維持し、特に複数のラッチが相互作用する可能性のある複雑な回路構成で、グリッチや意図しない変更なしで状態遷移が発生するようにするこのアライメントの要望。ラッチがセットとリセットコマンドに応答するときに制御することにより、システムは、システムの安定性とパフォーマンスを混乱させる可能性のあるレース条件やその他のタイミング関連エラーなどの問題を回避できます。

S-Rラッチの動作状態

その動作は、セットとリセット(R)の2つの制御信号の入力に依存します。ここでは、これらの入力がSRラッチの出力と状態にどのように影響するかを説明します。

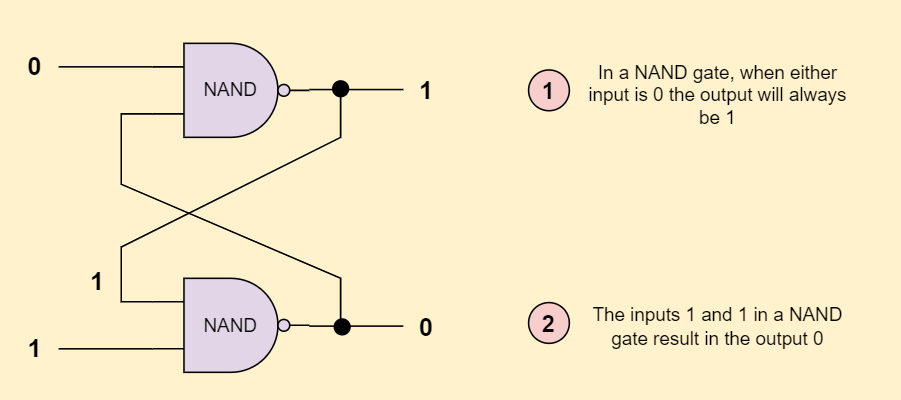

ケース1:条件を設定します

セットの入力が高(1)で、リセット(R)入力が低い(0)場合、ラッチはセット条件に入ります。この状態では、R入力に接続されたNANDゲートは、Sからの高い入力により低信号が出力されます。低い(0)。この状態は安定しており、入力が変更されるまでQを高く保ち、高状態を保存するラッチの能力を示します。

図3:設定状態

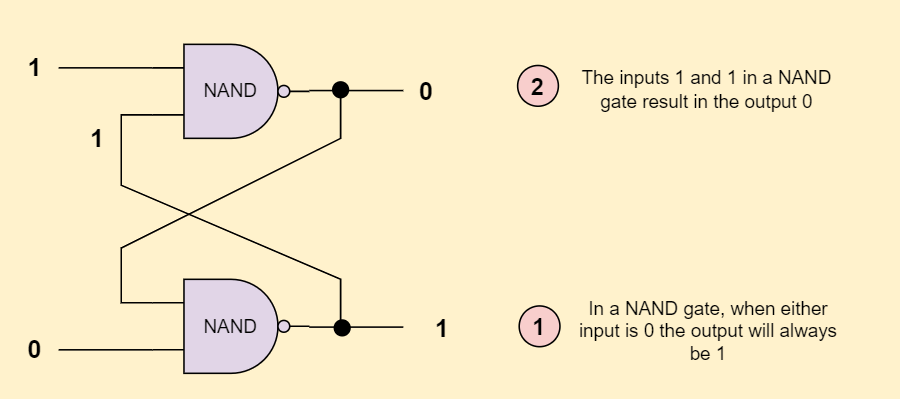

ケース2:リセット状態

Sが低く(0)、Rが高い場合(1)、ラッチはリセット条件に入ります。ここでは、Rの高い入力とSの低入力により、NANDゲートがRに接続されたNANDゲートが低信号を出力します。この低信号は、qを低(0)に、q-barからhigh(1)に設定し、ラッチを効果的にリセットします。これは、適切な入力が与えられたときにQで安定した低状態に戻るラッチの能力を示しています。

図4:リセット状態

ケース3:無効な状態

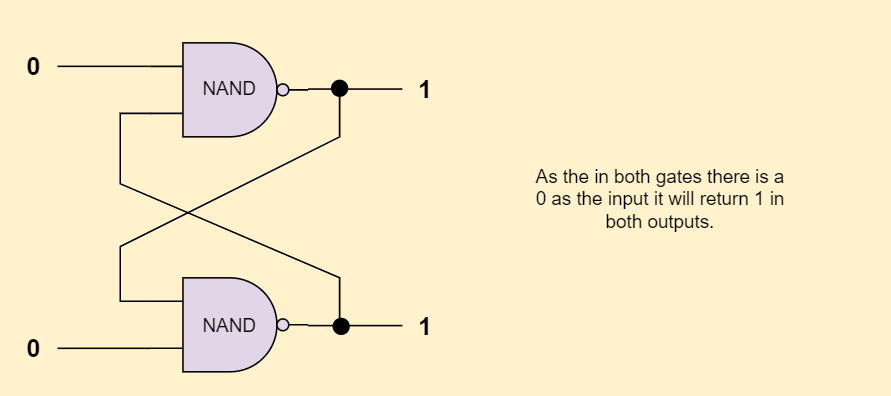

SとRの両方が低い場合(0)、NANDゲートへの両方の入力が低く、出力QとQ-BARの両方が高くなります。この状態は、QとQ-Barが常に反対であるべきであるという基本的なルールを破るため、無効または禁止されていると呼ばれます。このシナリオは、SRラッチの制限を強調し、適切な入力管理を通じてそのような不安定な状態を回避することの重要性を強調しています。

図5:無効な状態

ケース4:条件を保持します

両方の入力が高い場合(1)、出力は現在の入力ではなく、ラッチの以前の状態に依存します。これは保留条件として知られています。ここでは、QとQ-BARが変化しないままで、ラッチの最後の有効な状態を保存します。一部のアプリケーションでは、データの整合性が非常に重要なメモリストレージセルなど、変更なしで長時間ラッチ状態を維持できることが重要です。

図6:ホールド状態

真実のテーブルを備えたS-Rラッチ

このテーブルは、単なる理論的なツールではありませんが、サーキットデザイナーと学生の両方にとって実用的です。多くの条件下でラッチがどのように動作するかを見るのに役立ちます。以下に、SRラッチの包括的な真理テーブルを紹介し、その後、各条件の説明と実用的な洞察が続きます。

|

s |

r |

Q |

Qバー |

州 |

|

0 |

0 |

1 |

1 |

無効 |

|

0 |

1 |

0 |

1 |

リセット |

|

1 |

0 |

1 |

0 |

セット |

|

1 |

1 |

Q |

Qバー |

所有 |

チャート1:sr

ラッチトゥルーステーブル

各行の説明

条件を設定(s = 1、r = 0):この行は、Sが高く、rが低い場合、qが高(1)、q-barから低(0)に設定されることを示しています。これは、セットコマンドに対する回路の応答を反映して、「1」を効果的に保存します。

リセット条件(S = 0、r = 1):ここで、入力はリセット操作を示します。その結果、Qは低(0)にリセットされ、Q-BARは高(1)に設定されます。この状態は、「0」に戻るラッチの能力を示しています。

無効な条件(S = 0、r = 0):この条件では両方の出力が高くなります。これは、両方の出力が同一であるため、一般に回避されます。これは、QとQ-BARが常に反対であるべきであるというルールに違反するため、ラッチの不安定性または未定義の動作につながる可能性があります。

保持条件(S = 1、r = 1):このシナリオでは、ラッチは以前の状態を維持し、明示的に変更するように命じられない限り、最後のセット状態を保持する能力を示します。

実用的な洞察とヒント

出力の理解:QとQ-BARが理想的には補完されることを常に覚えておいてください。このルールからの逸脱(無効な状態で見られる)は、問題または誤解を示します。

無効な状態を避ける:設計者がSとRの両方が低い状況を防ぐように注意することが不可欠です。追加のロジックまたはインターロックを実装することは、この状態を防ぐのに役立ちます。

保留条件の利用:保留条件は、時間の経過とともにデータ保存を必要とするアプリケーションで特に便利です。データの整合性を維持することは、ラッチが誤ってセットまたはリセット状態に入らないようにすることに依存する可能性があります。

真実のテーブルの解釈:回路を設計またはデバッグするときは、真実の表を参照して、特に複数のラッチが使用される複雑な回路で、入力の変更が出力にどのように影響するかを予測します。

S-Rラッチの機能的ダイナミクス

S-R(Set-Reset)ラッチは、入力が正しく管理されている場合にのみうまく機能します。それがどのように機能するかを理解するには、異なる入力の組み合わせが出力、QおよびQ-BAR(Qの反対)にどのように影響するかを知る必要があります。

図7:S-Rラッチ

SET(S)とRESET(R)の両方が同時にアクティブになっている場合(S = 1とR = 1)、ラッチは「禁止状態」になり、出力、Q-BARの両方が0です。これは、通常、QとQ-BARが反対であるはずなので問題です。

通常の条件下では、ラッチを設定するために、S(Sを1に設定)をアクティブにし、R(Rを0に設定)を非アクティブ化します。これにより、Qが高くなり(1)、Q-barは低くなり(0)、ラッチが1を保存できることを示します。ラッチをリセットするには、r(rを1に設定)をアクティブにし、S(sを0にセット)を無効にします。これにより、Qが低くなり(0)、Q-Barは高くなり(1)、ラッチがそれ自体をクリアして0を保存できることを示す。

両方の入力が非アクティブ化されている場合(S = 0およびr = 0)、ラッチは最後の状態を設定またはリセットします。これは、継続的な入力を必要とせずにデータを保存したり、状態を維持するのに適しています。

人種条件は、S-Rラッチの動作を複雑にする可能性があります。これらのエラーは、出力が入力の変更のタイミングに大きく依存している場合に発生し、入力がほぼ同時に変更された場合、予測不可能な結果になります。これを防ぎ、ラッチが確実に機能するようにするために、時間遅延のメカニズムがよく使用されます。これらの遅延により、一方の入力が安定する時間があった後に1つの入力がアクティブになることを確認します。正確なタイミングが必要なデジタルサーキットでラッチを使用するには、一貫して実行され、安定した出力を維持する必要があります。これは、制御されたタイミングによって可能になります。

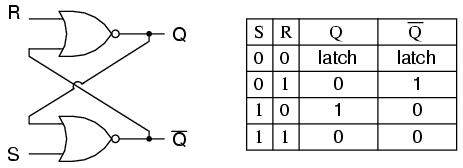

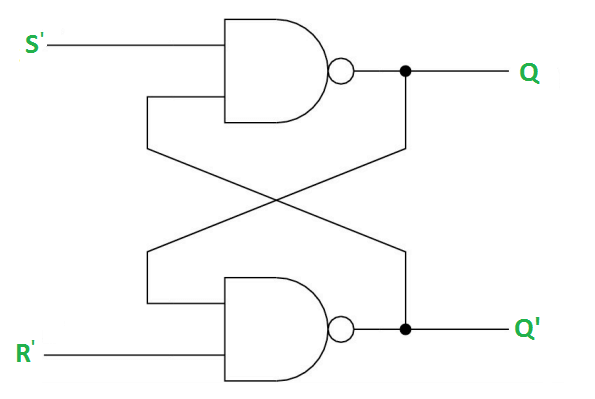

S-Rラッチのロジック図

SRラッチは、2つの主要な構成を備えた基本的なシーケンシャルロジック回路です。NORまたはNANDゲートです。各セットアップは、ラッチの仕組みに影響を与え、入力に応答し、さまざまな電子アプリケーションのカスタマイズを可能にします。

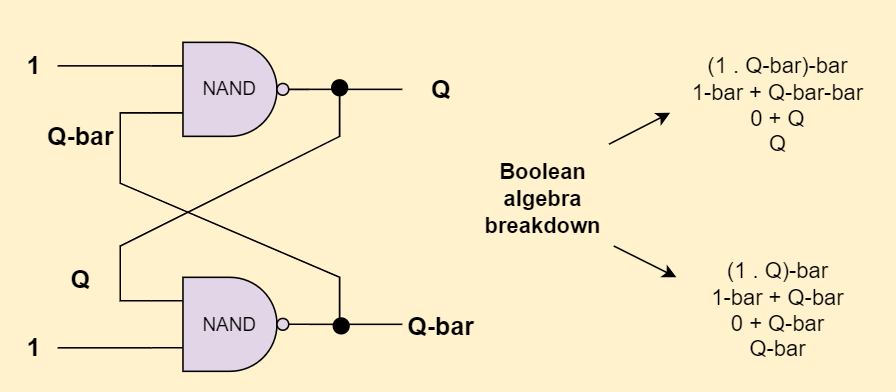

図8:ロジック図は、NANDゲートを使用したS-Rラッチを表しています

NANDゲートを使用した実装

Nand GatesでSRラッチを構築する場合、フィードバックループを使用して状態を維持します。このセットアップにより、両方の入力(SとR)が低い場合、ラッチは以前の状態を維持できます。両方の入力が高い場合を除き、NANDゲートは高く出力します。1つの入力が高く、もう1つの入力が低いと、ラッチの状態が変化します。両方の出力が低くなり、出力がもはや補完的ではない未定義の状態につながるため、同時にSとRの両方を同時に設定することを避けるのが最善です。NANDベースのSRラッチの不安定性を防ぐには、適切な入力管理が必要です。

NORゲートを使用した実装

SRラッチにNOR Gatesを使用すると、NANDゲートと比較して運用条件が変更されます。この構成では、両方の入力が高い場合、ラッチは状態を保持します。1つの入力が低く、もう1つの入力が高い場合、ラッチは状態を変更します。両方の入力が低い場合にのみ、ゲートは高く出力されません。このセットアップは、デフォルトの状態が両方の出力を低くする回路で役立ち、高入力条件下で予測可能な出力を確保します。ただし、両方の入力を同時に低く設定しないようにすることをお勧めします。これにより、出力が矛盾し、ラッチの信頼性が低下するためです。

図9:論理図は、NORゲートを使用したS-Rラッチを表しています

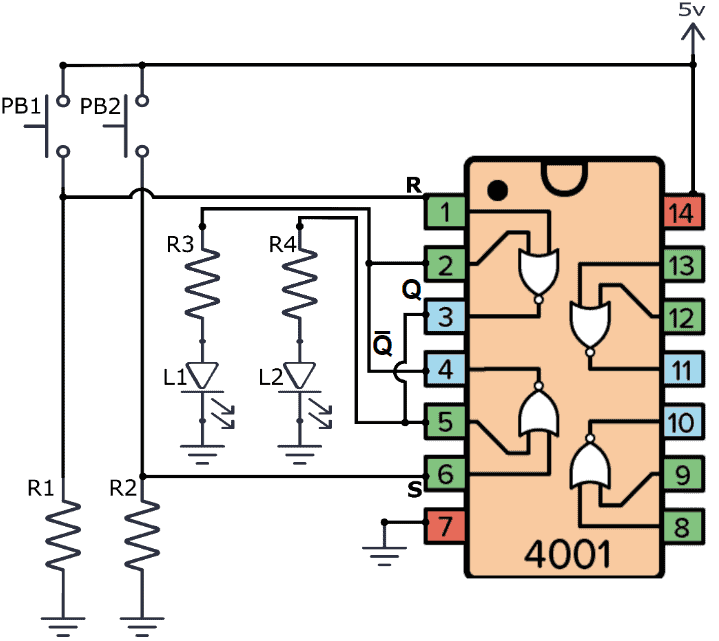

サンプル回路

SRラッチが実際の生活でどのように機能するかを探ることは、その有用性を示しています。良い例は、CD4001チップを使用した回路で、4つのゲートがあります。この回路は、SRラッチがボタンを押すなどの単純なアクションでLEDのようなデバイスを制御する方法を示しています。

この例では、CD4001チップのNORゲートがSRラッチを作成するためにセットアップされています。ラッチ状態を維持するために、2つのゲートがフィードバックループに接続されています。プッシュボタンは、セットおよびリセットの入力として回路に追加されます。ボタンを押すと、入力の状態が変更され、ラッチとLED状態が変更されます。たとえば、設定ボタンを押すとLEDを照らし、ボタンが解放された後でも点灯したままで、ラッチが状態を維持する方法を示します。

回路を改善するために、より多くのLEDを追加して、Q-BARの両方の出力状態を表示できます。これにより、ラッチがどのように機能するかを簡単に確認できます。これは、学習環境で非常に役立ちます。

図10:CD4001チップを使用したS-Rラッチ

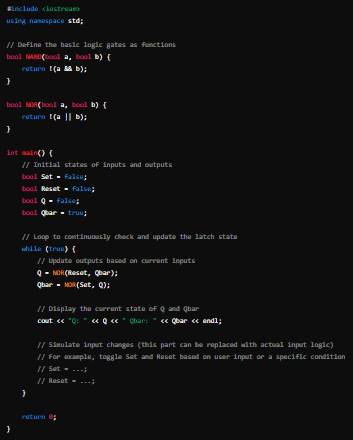

コード実装

SRラッチの運用ロジックをソフトウェアに変換することは、デジタルロジック設計がハードウェアと仮想シミュレーションの両方でどのように機能するかを示しています。C ++のようなプログラミング言語を使用することは、ハードウェアの動作を模倣するために必要な複雑なロジックとコントロールをサポートするため、効果的です。

C ++でSRラッチを作成するには、基本的なロジックゲートをハードウェアバージョンのように機能する関数として定義することから始めます。たとえば、NANDゲート関数は、その入力の操作と操作の反対を返します。同様に、NORゲート関数は、OR操作の反対を返します。これらの基本的な関数を使用すると、ラッチの回路図に基づいて、これらのゲート関数間にフィードバックループを作成することにより、SRラッチの動作をモデル化できます。

通常、コードには、入力の状態を継続的にチェックし(設定およびリセット)ループがあり、それに応じて出力(QおよびQ-BAR)を更新します。このループ内の条件ステートメントは、入力の変化が出力にどのように影響するかを決定し、SRラッチの物理的挙動を密接に模倣します。たとえば、入力とリセットの両方が低い場合、出力は同じままです。セットが高く、リセットが低い場合、出力Qが高くなり、Q-BARが低くなり、ラッチのセット条件を複製します。

これがこれがコードでどのように見えるかの簡単な例です。

図11:C ++のSRラッチ

このコードは、NORゲートを使用して単純なSRラッチを設定し、入力に基づいてラッチ状態を継続的にチェックおよび更新します。

SRラッチのアプリケーション

モーター動作における制御システム:モーター制御のためにシステムが必要とするSRラッチ。Start(S)とSTOP(R)Pushbutton Switchesを使用して、SRラッチは、スタートボタンが解放された後でもモーターを実行し続けます。このセットアップにより、モーターが停止するまで継続的に実行され、安全性と利便性が向上します。

メモリとデータストレージ:より大きなメモリ回路を作成するとき、SRラッチは、単一のデータを保存できるため、役割を果たします。デジタルコンピューティングにおけるメモリセルの基礎を形成するまで、更新されるまで安定した状態でデータを維持します。

信号制御と管理:制御信号アプリケーションでは、SRラッチは特定の条件が満たされるまで特定のビットを保持し、適切なシーケンスと操作のタイミングを確保します。信号処理とデータフローの精度はこれに依存します。

デバウンドサーキット:SRラッチは、機械式スイッチとボタンからの信号を安定化し、スイッチが押されたときに「バウンス」によって引き起こされる誤ったトリガーとエラーを防ぎます。これは、キーボードのようなデジタルインターフェイスに特に適合します。

デジタルシステムの基礎要素:電子機器のタイミングとシーケンスに適したフリップフロップとカウンターの設計は、SRラッチに大きく依存しています。また、迅速な状態切り替えのパルスラッチとしても使用されます。

特殊なアプリケーション:非同期システムでは、Dラッチなどのバリエーションが安全で信頼できるデータ転送に使用されます。同期2相システムでは、データラッチは通過カウントを減らし、効率を改善し、遅延を減らします。

エレクトロニクスにおけるより広範な影響:SRラッチは、電子装置内の省エネルギーの節約に参加している電力ゲーティングサーキットで広く使用されています。彼らは詳細なレベルで電力状態を管理し、デジタルシステムの全体的なエネルギー効率に貢献しています。

結論

S-Rラッチは、複雑なデジタルシステムにおける単純なロジック構造の重要性を示しています。さまざまなセットアップとそれがどのように機能するかを調べることにより、S-Rラッチがデータを安定させ、システムを効率的かつ信頼できるものにしていることがわかります。真実のテーブルとロジック図によって示されるさまざまな条件下で機能し、モーター制御からフリップフロップやカウンターなどの基本的なデジタルサーキットまで、いくつかの用途に適応できます。S-Rラッチは、コンピューターのメモリセルやデジタルインターフェイスの脱circuitsなど、多くの実用的なアプリケーションで適しています。フィードバックメカニズムと慎重な入力信号管理により、S-Rラッチは、より信頼性が高く効率的なデジタルシステムを設計するのに適しています。ソフトウェアシミュレーションを介してその機能を研究することで、理論的電子機器を実際のアプリケーションに接続し、S-Rラッチを新規および経験豊富な電子エンジニアの両方にとって重要なトピックにします。

よくある質問[FAQ]

1. SRラッチの目的は何ですか?

SRラッチは、単一のデータを保存するために使用されます。これは、デジタルサーキットのメモリの基本的な形式です。その主な機能は、入力信号によって変更されるまで少しの状態を保持することです。

2. SRラッチはアクティブな高または低いですか?

SRラッチは通常、アクティブな高さです。つまり、高い入力に応答します(ロジックレベル1)。入力s(set)とr(reset)が高い場合、出力の変化をトリガーします。

3. SRラッチの不利な点は何ですか?

SRラッチの主な欠点は、セットとリセットの両方の入力が同時に高くなっている無効な状態に対する感受性です。この状況は、未定義の出力につながり、信頼できないまたは予測不可能な動作をもたらす可能性があります。

4. SRラッチのルールは何ですか?

S(SET)が高く、R(リセット)が低い場合、出力Qは高く設定されます。

Rが高く、Sが低い場合、出力Qは低くリセットされます。

SとRの両方が低い場合、出力は以前の状態を保持します。

SとRの両方が高い場合、出力は未定義または無効です。

5. SRラッチのメモリとは何ですか?

SRラッチのメモリは、状態を変更するための入力を受信するまで、出力状態(高または低)を無期限に維持する能力を指します。これにより、シンプルなメモリストレージに最適な双方向のデバイスになります。

6. SRラッチの出力は何ですか?

SRラッチには、QとQ '(Q-BAR)の2つの出力があります。Qは現在の状態を表し、Q 'はQの逆です。Qが高い場合、Q'は低く、逆も同様です。

7.ラッチはどこで使用しますか?

短期のデータストレージまたは状態保持が必要な場合、さまざまな種類のアプリケーションでラッチが採用されます。これには、フリップフロップ、レジスタ、メモリユニット、およびデータの同期と回路ホールド機能を必要とするシステムのデータストレージが含まれます。