Tトリガーナレッジガイド - 長所と短所、それがどのように機能するか、タイプ

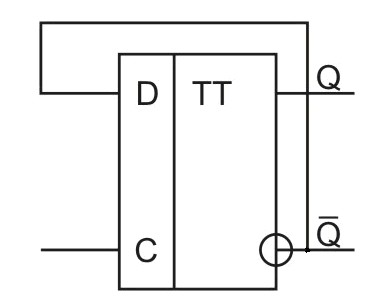

T-flip-flopsは、JKフリップフロップに似ています。jとkの入力を接続することにより、tフリップフロップを導出できます。Dフリップフロップのように、クロックとともに外部入力は1つだけです。

カタログ

T-flip-flopsの仕組み

ビーチサンダル 2つの安定した状態を示すデジタルオートマトンの最も単純なデバイスです。1つの状態は「1」の値を保持し、もう1つの状態は「0」です。デバイスの状態とその中に保存されているバイナリ情報は、出力信号(直接および逆)によって決定されます。論理出力に対応する直接出力に電位が設定されている場合、デバイスは単一トリガー状態にあります(逆出力の電位は論理ゼロに対応します)。直接出力に可能性がない場合、デバイスはゼロ状態にあります。

T-flip-flopsの種類

T-flip-flopsには主に2つの品種があります。

非同期Tトリガー

同期Tトリガー

両方のタイプのT-flip-flopsも同様に動作します。唯一の違いは、ある状態から別の状態に移行するプロセスです。非同期型はこの遷移を直接実行しますが、同期型はこの信号に基づいて動作します。

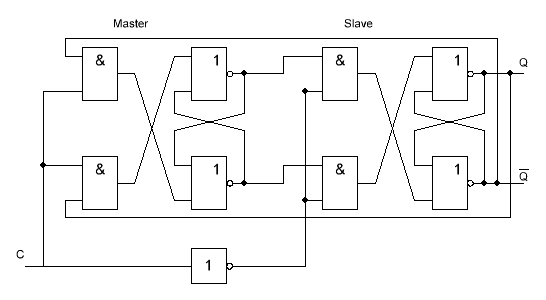

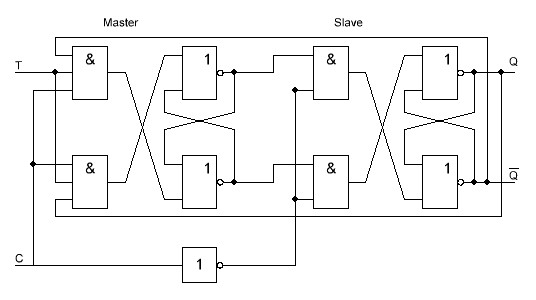

クロック入力が常に高い(1)あるシナリオを評価する場合、トグル(t)入力の2つの潜在的な状態(1)または低(0)のいずれかを考慮する必要があります。各状態の結果と関連する論理ゲートの相互作用を詳述しましょう。

ケース1:t = 0

- 出力条件:ここでは、gate1とgate2の両方がt(0に設定)に接続されているゲートです。

- GATE1およびGATE2出力:ANとGATE出力0の入力が0の場合、他の入力に関係なく、GATE1とGATE2の出力は常に0になります。

- gate3/q(n+1)ロジック:gate3は、gate1の出力の影響を受けます。GATE1が0を出力すると、gate3のロジック方程式はnot(0またはnot q)に簡素化され、qになります。

- gate4/q(n+1) 'ロジック:gate4は同様のパターンに従い、qまたはqではないように単純化しない(0またはq)を生成します。

ケース1概要:

- gate1 = 0およびgate2 = 0を仮定し、およびゲートとゲートの特性を利用すると(0の入力は0の出力になります)、操作は簡単です。

- GATE3/Q(n+1)はqとして計算し、現在の状態を維持します。

- gate4/q(n+1) 'q'は、現在の状態を補完します。

ケース2:t = 1

- 出力条件:tが1に設定されている場合、GATE1とGATE2の入力は、他のロジック操作の出力を反映し、出力に影響を与えます。

- gate1およびgate2出力:gate1は、現在の状態qに直接接続し、gate2はqまたはq 'ではありません。

- gate4/q(n+1) 'ロジック:ここで、式はand gateの入力が反対(qおよびqではなく)であり、0になるため、式が簡素化されます。

- gate3/q(n+1)ロジック:一方、gate3はqまたはq 'ではなく、q'ではなく出力(qと0)を扱い、qまたはqではないように単純化します。

ケース2の概要:

- ロジックのセットアップは、興味深い相互作用につながります。

- gate1 = q、gate2 = q '、その後のロジックプロセスに影響します。

- gate4/q(n+1) 'は0として直接計算します。qとqではない間の操作は真ではないためです。

- GATE3/Q(n+1)はq 'として計算します。これは、tが0の場合の前の状態からのトグルです。

Tフリップフロップトゥルーステーブル

|

clk |

t |

Q(n+1) |

州 |

|

|

0 |

Q |

変更はありません |

|

|

1 |

Q ' |

トグル |

この真理テーブルを使用して、Tフリップフロップ用の特徴的なテーブルをコンパイルします。The Truth Tableでは、入力tと1つの出力q(n+1)のみが表示されます。ただし、特性表には、2つの入力TとQN、および1つの出力Q(n+1)が表示されます。

上記のロジック図から、QNとQN 'が2つの相補的出力であり、GATE3とGATE4の入力としても機能することは明らかです。n+1)次の状態の出力として。

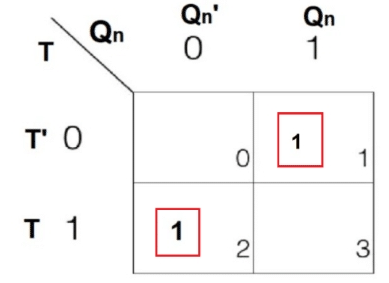

特徴的なテーブルを完了すると、2変数Kマップを構築して特性方程式を導き出します。

|

t |

Qn |

Q(n+1) |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0

|

Kマップから、2つのペアを取得します。両方を解くと、次の特性方程式が得られます。

q(n + 1)= tqn ’ + t’qn = t xor qn

T-flip-flopsの使用の利点

デジタルサーキットでは、T-Flip-Flopsは、機能と統合を簡素化するいくつかの重要な利点を提供します。

- 単一の入力シンプルさ: T-flip-flopsには入力が1つしかなく、操作が簡素化されます。この単一の入力は、高状態と低い状態を切り替えることができ、回路設計にシームレスに統合され、他のデジタルサーキットと簡単に接続できます。

- 無効な状態はありません: T-flip-flopsには無効な状態がなく、デジタルシステムでの予測不可能な動作を防ぐのに役立ちます。この信頼性は、一貫したシステムパフォーマンスを維持するために重要です。

- 消費電力の削減: 他のフリップフロップと比較して、T-flip-flopsの消費電力は少なくなります。このエネルギー効率は、ポータブルデバイスのバッテリー寿命を延長し、大規模なデジタルシステムのエネルギーコストを削減するのに有益です。

- 双安定操作: 他のフリップフロップと同様に、T-flip-flopsは双安定操作を備えています。つまり、入力信号によってトリガーされるまで、どちらか(0または1)を無期限に保持できることを意味します。この特性は、単一ビットデータの安定した長期的な保存を必要とするアプリケーションに不可欠です。

- 簡単な実装: T-flip-flopsは、基本的なロジックゲートを使用して簡単に実装できます。このシンプルさにより、多くのデジタルシステムにとって経済的に実行可能な選択肢となり、システム全体のコストを削減できます。

T-flip-flopsの制限

これらの利点にもかかわらず、T-Flip-Flopsには、特定のアプリケーションへの適合性に影響を与える可能性のあるいくつかの制限もあります。

- 倒立出力: T-flip-flopsの出力は、その入力の反対であり、タイミングロジック回路の設計を複雑にし、設計をより複雑にすることができます。設計者は、正しい回路の動作を確保するためにこれを考慮する必要があります。

- 限られた機能: T-flip-flopsは、1つの情報しか保存できず、追加や乗算などの複雑な操作を実行することができず、基本的なメモリタスクでの使用を制限します。

- グリッチに対する感受性: T-flip-flopsは、入力信号のグリッチやノイズに敏感であり、予期しない状態の変更を引き起こす可能性があります。この感度は、特に高い電子干渉を伴う環境で、デジタルシステムで予測不可能な動作につながる可能性があります。

- 伝播遅延: すべてのフリップフロップと同様に、T-flip-flopsは伝播遅延に遭遇し、厳密なタイミング制約を備えたシステムにタイミングの問題をもたらす可能性があります。これらの遅延は、タイミングエラーを回避し、信頼できる操作を確保するために、システム設計中に考慮する必要があります。

アプリケーション

T-flip-flopsは、以下を含むさまざまな実際のアプリケーションで使用されます。

- 周波数分割: T-flip-flopsは、クロック信号の周波数を半分にするためによく使用されます。フリップフロップの状態を各クロックパルスで切り替えることにより、入力信号の周波数を効果的に2だけ分割し、正確なタイミングとデジタルクロック、周波数シンセサイザーに最適です。

- 周波数倍: 逆に、T-flip-flopsを使用して、周波数2倍と呼ばれるクロック信号の周波数を2倍にすることもできます。これは、入力信号の2倍の出力周波数を生成するセットアップにフリップフロップを設定することによって達成されます。

- データストレージ: T-flip-flopsは、単一のデータビットを保存するための基本的なビルディングブロックとして使用できます。ここでは、さらに処理または送信するためにデータを一時的に保存する必要があります。これにより、シフトレジスタやストレージデバイスなどのアプリケーションで非常に便利になります。

- カウンター: T-flip-flopsのもう1つの重要なアプリケーションは、バイナリカウンターの作成です。これらは、他のデジタルロジックゲートと相互接続して、設計要件に基づいてカウントを増加または減少させるカウンターを構築できます。