JKフリップフロップの革新的なガイド:真実のテーブル、メカニズム、戦略的アプリケーションの分析

この記事では、基本的な構造と入出力関係から、詳細な運用力学を通じて、複雑なデジタルシステムにおける戦略的実装まで、JKフリップフロップのアーキテクチャ、操作、および多様なアプリケーションについて説明します。談話は、エッジトリガーとレベルのトリガーされたバリアントを区別し、同期環境と非同期環境でそれぞれのユーティリティを分析することにまで及びます。カタログ

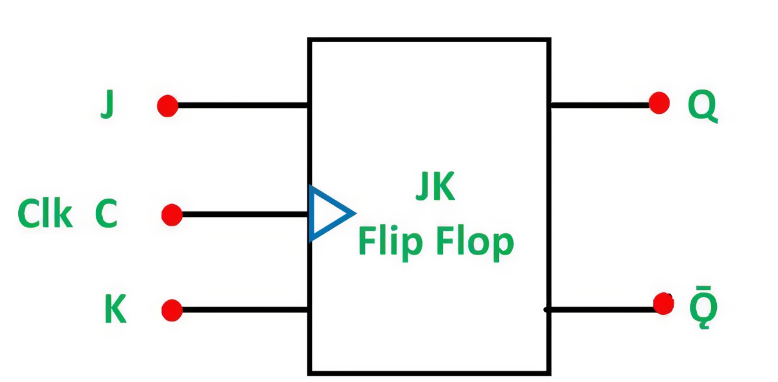

図1:JKフリップフロップ

JKフリップフロップの基本

JKフリップフロップは、デジタルエレクトロニクスの基本的なコンポーネントであり、1つの情報を保存するように設計されています。フィードバックを追加することにより、よりシンプルなSRフリップフロップの上に構築されます。これは、出力が不安定になる「人種条件」として知られるエラーを防ぐのに役立ちます。

このフリップフロップには、j(set)とk(リセット)の2つの主要な入力と、qとその補体q 'の2つの出力があります。これらの出力は、現在の状態とその反対を継続的に反映しており、回路がリアルタイムの入力の変更を調整および応答できるようにします。

JKフリップフロップは、入力値に基づいて特定の方法で動作します。

•JとKの両方が0の場合: フリップフロップは現在の状態を保持します。変更は発生しません。

•JとKの両方が1の場合: フリップフロップはその状態を切り替えます。qが0の場合、1になります。Qが1の場合、0に切り替わります。このトグルアクションは、JKフリップフロップをよりシンプルなデザインと区別する重要な機能です。

•jが1、kが0の場合: フリップフロップは状態を設定し、Qを1に等しくします。

•jが0で、kが1の場合: フリップフロップがリセットされ、Qが0に等しくなります。

JKフリップフロップの操作

JKフリップフロップは、入力信号とクロックパルスに対する調整された応答を通じてメモリとタイミングを管理することにより、デジタル回路で重要な役割を果たします。その動作は、クロック信号に対するjおよびk入力のタイミングに大きく依存しており、出力状態(qおよびq̅)がどのように変化するかを決定します。この同期により、さまざまな回路アプリケーションでフリップフロップが予測可能に動作することが保証されます。フリップフロップは、これらの状態の変更を管理するためにNANDまたはゲートに依存しています。

現在の状態を保持します-J入力とKの両方の入力が低い場合(0)、フリップフロップは現在の状態を維持します。ロジックゲートは出力を効果的に「ロック」し、以前の状態(高または低い)が維持されるようにします。この保持機能は、特定の変更が必要になるまでデータが安定したままでなければならないアプリケーションでは深刻です。

出力を高く設定する(SET状態) - クロックパルスが発生し、jが高く(1)、Kが低いままである場合(0)、ロジックゲートはフリップフロップを設定するように調整します。これにより、出力qが高状態に駆動されます(1)。これは、回路が高出力をトリガーする必要がある状況で有用です。たとえば、デバイスのアクティブ化やメモリに「1」を保存するなどです。

出力を低くクリアする(リセット状態) -Jが低い(0)、kがクロックパルス時に高(1)である場合、フリップフロップはリセット状態に遷移し、Qを低くすることを強制します(0)。このリセットアクションは、メモリからデータをクリアするなど、操作を完了した後にデフォルトまたはクリア状態を必要とする回路でよく使用されます。

出力の切り替え -JとKの両方が高くなると、Flip-Flopのユニークな機能が現れます(1)。クロックパルスが到着すると、フリップフロップが切り替わり、出力を現在の状態から反対側の状態に切り替えます。Qが高い場合、それは低くなり、Qが低い場合、それは高くなります。このトグル関数は、状態を自動的に交互に交互に行う必要があるカウンターやデバイスなどのアプリケーションで執行しています。

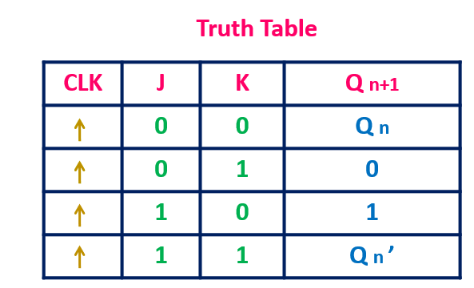

図2:JKフリップフロップトゥルーステーブル

JKフリップフロップトゥルーステーブル分析

JKフリップフロップの真理テーブルは、クロックパルスと同期して異なる入力信号にどのように反応するかを視覚化するための重要なツールです。このテーブルは、さまざまな入力条件に基づいてフリップフロップの出力がどのように変化するかを示すことにより、デジタルサーキットの設計とトラブルシューティングの両方に役立ちます。

•jとkの両方の低い(j = 0、k = 0): 両方の入力が0の場合、フリップフロップは現在の状態を保持します。Qが高くても低いかどうかにかかわらず、変更されません。これは、特定の変化がトリガーされるまで現在の状態を保存することが適切なインメモリ要素など、安定したデータ保持が必要な回路で注目に値します。

•j high、k low(j = 1、k = 0): jが1、kが0の場合、フリップフロップは出力qを高に設定します(1)。この設定条件は、デバイスの電源を入れたり、ロジック回路でシーケンスを開始したりするなど、操作をアクティブにするために正確なトリガーを必要とするアプリケーションで役立ちます。

•j low、k high(j = 0、k = 1): jが0で、Kが1で、フリップフロップがリセットされ、Qが低くなります(0)。このリセット関数は、データをクリアするときやプロセスの初期化など、デフォルトの状態に戻る必要があるシステムでは深刻です。

•JとK Highの両方(J = 1、K = 1): 両方の入力が高い場合、フリップフロップはその状態を切り替えます。Qが高い場合、それは低くなり、Qが低い場合、それは高くなります。この切り替えの動作は、周波数仕分けやカウンターなど、状態間を交互に行う必要があるデバイスにとって重要です。

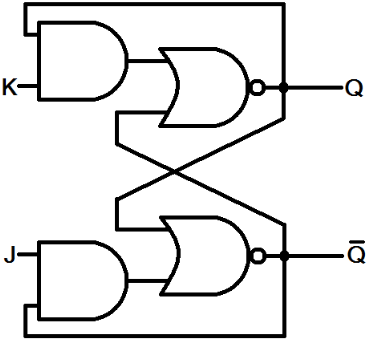

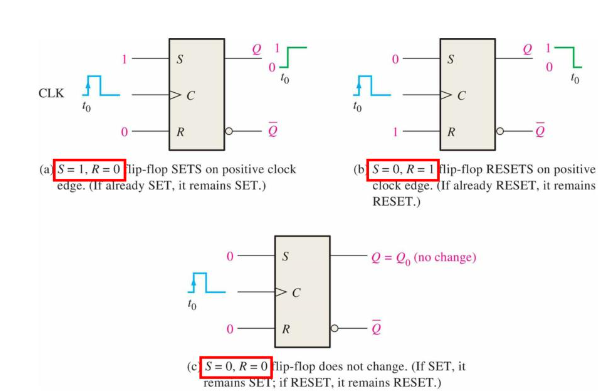

図3:JKラッチ

JKラッチ操作と使用に関する洞察

JKラッチは、JKフリップフロップと同様に動作しますが、クロック信号は必要ありません。JKラッチは、時計のエッジを待つ代わりに、入力の変更に継続的に応答し、「レベルに敏感」にします。これは、入力(jとk)が安定している限り、出力はリアルタイムで変化し、入力条件に基づいてすぐにフィードバックを提供することを意味します。

クロック信号が変化した場合にのみ出力を更新するエッジトリガーされたJKフリップフロップとは異なり、JKラッチは入力シフトとして即座に出力を調整します。この一定のリアルタイムの応答性は、時計の同期によって引き起こされる遅延なく即時のアクションが望まれるシナリオでは価値があります。

ノイズフィルター: 不要なノイズをすばやく除外する必要があるデジタル回路では、入力変化に対するJKラッチの即時反応は影響力があります。クロックパルスを待たないため、ノイズが検出されるとすぐに出力を調整して、信号補正の遅延を防ぎます。

シンプルなメモリ要素: JKラッチは、複雑でクロックされた制御を必要としないシステムの基本メモリユニットとして機能します。入力が変わらない限り、ラッチは出力を安定させたため、現在の状態を効果的に保持します。これは、クロック操作のオーバーヘッドなしで情報を保持する必要がある回路に役立ちます。

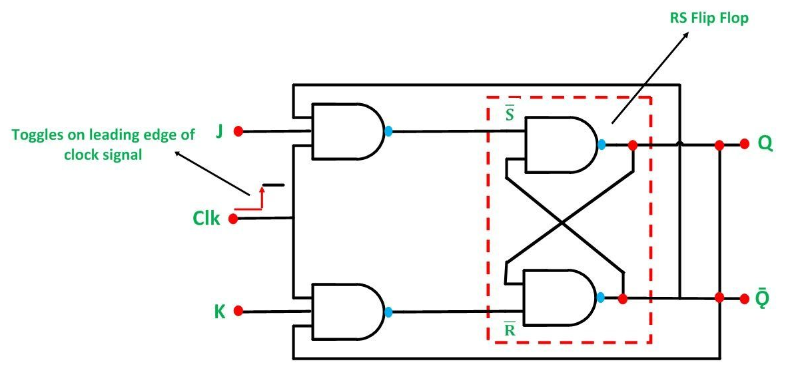

図4:JKフリップフロップのタイミング図分析

JKフリップフロップのタイミング図を分析します

JKフリップフロップのタイミング図は、クロックのパルス遷移と同期して、出力が異なる入力にどのように応答するかの視覚的な内訳を提供します。この図は、クロック信号(CLK)と入力(JおよびK)の関係と、それらが出力(QおよびQ ')に集合的にどのように影響するかを示しています。これは、シーケンシャル状態にわたるフリップフロップの動作をマッピングするのに役立ち、その動作を理解しやすくします。

まず、図 出力は、クロックパルスの上昇または下降エッジでのみ更新されることを強調表示します。エッジトリガーとして知られるこの機能は、JKフリップフロップの操作に支配的です。入力がjとkが変化したとしても、クロックエッジが発生するまで出力が変化しないままであり、予測可能で安定した遷移を保証することを示しています。

次に、図が入力jとkのバリエーションをマッピングすると、視覚的に 各入力の組み合わせが出力にどのように影響するかを示します。 たとえば、jとkの両方が低い場合(0)、出力は現在の状態を保持します。jが高く、kが低い場合、出力が設定されます。この明確な視覚表現は、ユーザーがフリップフロップがリアルタイムでさまざまな入力の組み合わせにどのように反応するかを理解するのに役立ちます。

ついに、 タイミング図は、保持、設定、リセット、または切り替えなど、異なる出力状態間の遷移を明確に示しています。各状態の変更は、入力条件とクロックエッジに直接結び付けられ、回路の設計とトラブルシューティングに焦点を当てている因果関係の関係を示しています。

JKフリップフロップの汎用性の高いアプリケーション

JKフリップフロップは、柔軟性と信頼性で知られている幅広いデジタルシステムのコアコンポーネントです。複雑なロジック操作を処理する能力により、次のようないくつかの重要なアプリケーションで必要になります。

図5:メモリストレージ

JKフリップフロップは、個々のデータを保存するために一般的に使用され、メモリアレイとレジスタに基本的な要素になります。各フリップフロップが少し保持され、信頼できるデータストレージが確保されます。これは、より大きなメモリシステムの設計に有益です。

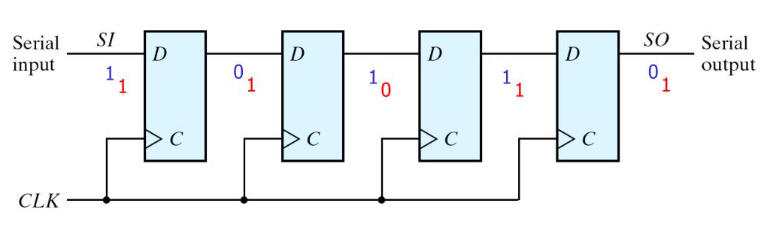

図6:カウンターとシフトレジスタ

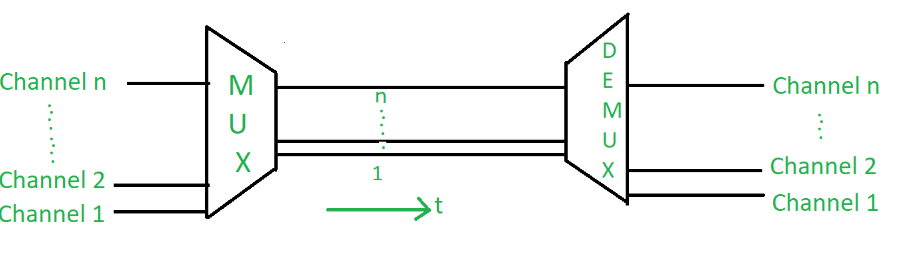

JKフリップフロップは、シーケンス操作において動的です。これらは、イベントやパルスをカウントするためのカウンターや、シリアルデータを並列形式に変換するためのシフトレジスタで広く使用されています。これにより、通信システムなどのプロセスのさまざまな段階でデータを管理および操作するのに役立ちます。

図7:周波数除算

信号処理では、JKフリップフロップが周波数分割によく使用されます。各クロックパルスで状態を切り替えることにより、入力信号の周波数を分割し、より遅く、管理しやすいクロック信号を作成します。これは、タイミング制御が必要な時計信号管理などのアプリケーションでは注目に値します。

図8:同期

JK Flip-Flopsは、システムの異なる部分が調整された方法で一緒に動作するようにすることにより、複数のデジタルプロセスを同期するのに役立ちます。これらは、さまざまなコンポーネントがタイミングされた信号に正しく応答し、システム全体を同期させることを保証します。

図9:JKフリップフロップ:エッジトリガーとレベルトリガー

さまざまなタイプのJKフリップフロップ

JKフリップフロップには、エッジトリガーとレベルトリガーの2つの主要なタイプがあり、それぞれ異なる運用要件向けに設計されています。

エッジトリガーJKフリップフロップ: クロック信号が低いものから高縁から(上昇)または高から低(下向きのエッジ)に移行する場合、特定のポイントでのみ状態を変更します。この特性により、正確なタイミングがしつこいシステムに理想的です。状態の変更は時計の端で正確に発生するため、これらのフリップフロップはすべての更新がクロックパルスと同期して発生することを保証します。この予測可能な動作は、デジタルクロック、レジスタ、およびほとんどのシーケンシャル回路などの厳密に制御された環境で動的です。ここでは、各変更のタイミングは、システムの安定性を維持し、操作が同期されるようにするために深刻です。

レベルトリガーJKフリップフロップ: 動作は異なり、クロック信号が高または低いかどうかにかかわらず、特定のレベルにある限り、入力信号に反応します。彼らは特定の時計の移行を待つことはありません。代わりに、入力が必要な条件を満たしている限り、フリップフロップは状態を変更します。この動作により、レベルトリガーされたフリップフロップは、入力が通常のクロックパルスと一致しない場合がある非同期システムに適しています。それらは、入力が予測不可能なシステムで柔軟性を提供したり、特定の信号処理タスクや、入力の変更に直ちに反応しなければならない監視システムなど、不規則な間隔に到達します。

JKフリップフロップの長所と短所

JKフリップフロップはいくつかの利点を提供しますが、デジタルシステムを設計する際に慎重に計量する必要があるトレードオフも付属しています。

|

長所 |

|

|

汎用性 |

JKフリップフロップは非常に柔軟で缶です

メモリストレージ、カウンター、および

制御システム。異なる入力に基づいて切り替え、設定、またはリセットできます

条件、それらを幅広いアプリケーションに適しています

州の移行を正確に制御する必要があります。 |

|

自己修正メカニズム |

JKの傑出した機能の1つ

Flip-flopsは組み込みのフィードバックループであり、論理的な修正に役立ちます

動的に状態。この自己修正により、回路が残ることが保証されます

入力が急速に変化した場合でも、操作中に安定します。 |

|

人種条件の緩和 |

よりシンプルなフリップフロップとは異なり、JKフリップフロップ

人種の状態を防ぐように設計されています - 出力がなる場所

競合する入力信号による不安定。維持するこの能力

一貫した出力は、高速および順次入力の変更の下であっても、を改善します

回路の信頼性。 |

|

短所 |

|

|

複雑なデザイン |

JKフリップフロップはより複雑です

基本的なフリップフロップ。彼らの設計には、追加のロジックゲートと入力が必要です

監視。回路の設計がより困難になる可能性があり、

特にシンプルさが望ましいシステムでのトラブルシューティング。 |

|

伝播遅延 |

州の管理に使用される内部ゲーティング

遷移は、信号を処理できる速度の遅延を導入します。で

高速アプリケーションでは、この遅延は全体的なタイミングに影響を及ぼし、減速する可能性があります

回路のパフォーマンス。 |

|

より高い消費電力 |

それらの複雑さとそうする必要があるため

常に入力条件を監視する、JKフリップフロップをより多くのパワーを消費する

よりシンプルなフリップフロップと比較してください。大規模なシステムまたは電力に敏感

アプリケーション、このより高い電力需要は欠点になる可能性があります |

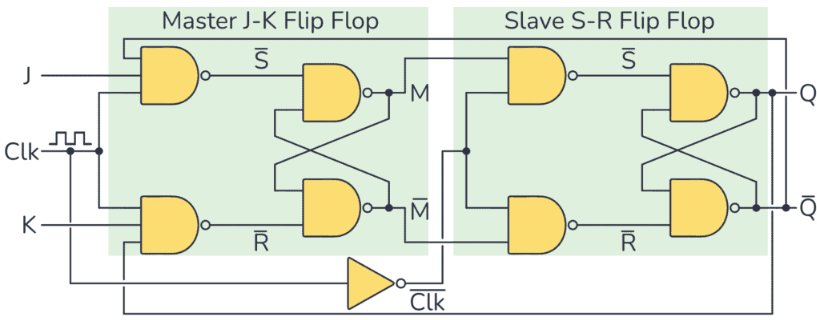

図10:マスタースレーブJKフリップフロップ

マスタースレーブJKフリップフロップのデコード

マスタースレーブJKフリップフロップは、2段階のプロセスを使用して入力と出力をより効率的に管理することにより、標準のJKフリップフロップに見られるレースアラウンド状態を解くように設計されています。

マスターステージと呼ばれる最初のステージは、クロック信号が上昇または下降のいずれかで特定のエッジに達すると、入力値をキャプチャします。この時点で、入力データがロックされています。つまり、入力へのさらなる変化は、次のクロックサイクルまでキャプチャされた状態に影響しないことを意味します。この段階により、フリップフロップが同じクロックサイクル中の後続の変化に影響されることなく、正しい入力を登録することが保証されます。

マスターステージが完了すると、スレーブステージが登場します。このステージは、マスターステージによってキャプチャされたデータに基づいて出力を更新しますが、次のクロックエッジでのみです。入力キャプチャを出力アップデートから分離することにより、スレーブステージは、マスターステージが入力を完全に処理するまで出力が安定したままであることを保証します。これにより、クロックサイクル中の出力の時期尚早または意図しない変化を防ぎます。

なぜマスタースレーブ構成が重要なのですか?

2段階のプロセスは、JKフリップフロップの動作を安定させ、特に両方の入力が高く保持されている場合、より単純な構成で発生する可能性のある不要な振動または変動を防ぎます。出力の変更からの入力処理を切り離すことにより、マスタースレーブ構成により、タイミングが価値がある状況であっても、出力が予測可能で安定したままであることが保証されます。

JKフリップフロップの状態に関するレースに対処します

JKフリップフロップでは、両方の入力、JとKが高く、クロック信号があまりにも長い間アクティブのままである場合、JKフリップフロップでレースアラウンド条件が発生します。これにより、出力が連続的に切り替えることにつながり、不安定な動作を引き起こし、回路の信頼性を破壊する可能性があります。

マスタースレーブセットアップは、2段階のプロセスを使用して、レースアラウンドの問題を防ぎます。マスターステージは、クロックエッジの入力値をキャプチャしてロックします。スレーブステージは、次のクロックエッジで出力を更新し、入力が完全に処理されるまで出力が変更されないようにします。このアプローチは、たとえ入力が長期間高く維持されたとしても、出力が制御不能に切り替えるのを効果的に防止します。

レースアラウンド条件を回避する別の方法は、クロックパルス期間を調整することです。フリップフロップの伝播遅延よりもクロックパルスを短くすることにより、同じクロックサイクル内で状態が複数回変化しないようにすることができます。これにより、フリップフロップが1つのサイクル中に繰り返し切り替えることを防ぎ、出力を安定させます。

JKフリップフロップでのスイッチングのダイナミクス

JKフリップフロップのスイッチング動作は、主にクロック信号と入力レベル(JおよびK)のタイミングによって駆動されます。フリップフロップは、クロック信号の正のエッジに存在する入力に基づいて状態を変更します。この危険な瞬間に、フリップフロップは入力を評価し、それに応じて出力を更新します。

クロック信号が立ち上がりエッジに当たると、JKフリップフロップはjおよびk入力の現在の状態を読み取ります。値に応じて、フリップフロップは出力を保持、設定、リセット、または切り替えます。

デジタル時計: 精度はデジタルクロックのすべてであり、JKフリップフロップは、状態の変更が正確なクロック間隔でのみ発生するようにすることにより、この精度を維持するのに役立ちます。

シーケンシャルロジックテスター: ロジック回路の機能をテストするシステムでは、JKフリップフロップが各コンポーネントが特定のタイミングされた信号に正しく応答することを確認する役割を果たします。

その他の時間に敏感なシステム: 通信システムやデータ処理ユニットなどのタイミングが危険なさまざまなデジタルアプリケーションでは、JKフリップフロップにより、状態の遷移が時計と同期して発生し、タイミングエラーが防止されます。

結論

JKフリップフロップは、デジタル回路設計の究極の要素として際立っており、メモリストレージから周波数分割、デジタルプロセスの同期に至るまでの幅広いアプリケーションに必死に汎用性と精度のブレンドを提供します。マスタースレーブアレンジメントなどの革新的な構成を介して人種条件を軽減する能力は、固有の設計上の課題を解決する際の適応性を強調しています。同様に、正確な状態遷移を確保する上でのフリップフロップの重大な役割は、信頼できる効率的なデジタルシステムの作成と維持に必要な性質を強調しています。テクノロジーが進むにつれて、JKフリップフロップの進化する設計とアプリケーションは、デジタルエレクトロニクスの境界をより洗練された堅牢なアーキテクチャに押し上げる際に引き続き重要です。

よくある質問[FAQ]

1. JKフロップフロップのアプリケーションは何ですか?

JKフリップフロップは、さまざまなタスクのためにデジタルエレクトロニクスで広く使用されています。

タイミングアプリケーション: 特定の構成で接続すると、遅延要素またはタイマーとして機能します。

カウンターとレジスタ: 各クロックパルスで状態を切り替えることにより、順次ロジック回路で究極のさまざまなカウンターとシフトレジスタの設計に使用されます。

メモリストレージ: 計算アプリケーションにビットを保存するのに役立つ、メモリストレージの基本単位を提供します。

2. JKフリップフロップは真実のテーブルでどのように機能しますか?

JKフリップフロップには、2つの入力(JとK)とクロック信号があります。その操作は、入力状態に基づいて異なり、時計に同期されています。

•j = 0、k = 0:出力は変更されません。

•j = 0、k = 1:出力は0にリセットされます。

•j = 1、k = 0:出力は1に設定されています。

•j = 1、k = 1:出力は切り替えます(つまり、0の場合、1になり、その逆になります)。

3. JKフリップフロップとは何ですか?それは機能していますか?

JKフリップフロップは、SRとTフリップフロップの特性を組み合わせています。JK入力を効果的に使用することにより、SRフリップフロップで見られる「禁止」状態を回避します。

フリップフロップの状態は、入力jとkによって制御されます。これにより、クロックパルスの上昇または下向きのエッジと同期して、出力が保持、リセット、設定、または切り替えが必要かどうかが判断されます。

4.ラッチとフリップフロップのアプリケーションは何ですか?

データストレージ: ラッチとフリップフロップは、レジスタとメモリアレイ内のデータストレージに深刻です。

周波数分割: クロックエッジで状態を変更する能力により、周波数仕切りで使用され、シリーズの各ステージで周波数を半分にします。

ステートマシン: 基本的に、シーケンシャルロジックと制御回路を実装するために使用される有限状態マシンを設計します。

デボンシング: 機械式スイッチとボタンからの信号を安定させるために使用され、単一のクリーンな遷移を確保します。

5.フリップフロップは何に使用されていますか?

バイナリストレージ: 各フリップフロップはデータを1ビット保存し、バイナリストレージデバイス用のビルディングブロックにします。

時計仕切り: 入力クロック周波数を2で割っており、デジタルクロックとタイミングアプリケーションで役立ちます。