完全な加算器への詳細なガイド

デジタルエレクトロニクスとコンピューターエンジニアリングの領域では、加算器は、より複雑な算術回路の構造と機能において極めて重要なビルディングブロックの1つを表しています。算術ロジックユニット(ALU)の積分コンポーネントとして、加算器は、基本的な算術からシステム操作に必要な複雑な論理タスクに至るまで、多数のコンピューティング操作を促進します。シンプルなハーフアダーからより複雑なフル加算器までさまざまなデザインは、デジタルシステム内の処理の効率と速度を高める上で重要な役割を果たします。この記事では、さまざまな種類のアドラーの詳細なアーキテクチャと機能的ニュアンスを掘り下げ、最新のコンピューティングテクノロジーにおける重要な役割を示し、デジタルロジック設計のより広範なコンテキスト内での運用ロジック、回路、アプリケーションを調査します。

カタログ

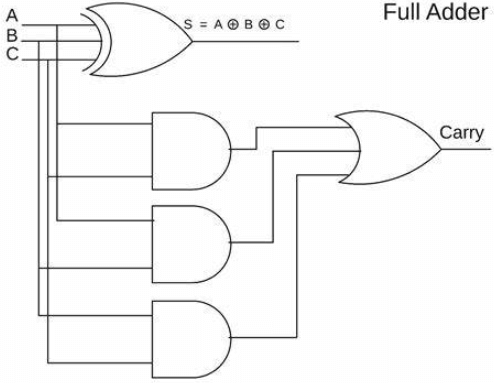

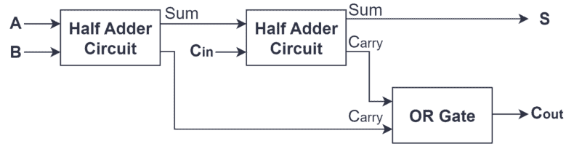

図1:フル加算器

加算器は、電子工学およびデジタルロジック設計の基本的なコンポーネントであり、より複雑なコンピューターシステムで中心的な役割を果たします。算術ロジックユニット(ALU)の一部として、Adderはさまざまな必須コンピューティングタスクを処理します。プロセッサ全体の効率とパフォーマンスは、加算器の設計と機能によって直接影響を受けます。

プロセッサでは、加算や減算などの基本的な算術操作だけでなく、より広範な範囲の論理操作にも使用されます。たとえば、プログラムを実行する場合、プロセッサは多くの場合、新しいメモリアドレスを計算する必要があります。これは通常、現在のアドレスを追加または減算することによって行われます。これは、ADDERが行ったタスクです。それらは、カウンターを増加および減少させることにより、ループ反復の数と全体的なフローを制御します。テーブルインデックスなどのより複雑なアプリケーションでは、加算器はオフセットを計算することでデータをすばやく見つけます。これは、データベース管理システム、コンパイラ構築、および大規模なデータ処理にとって重要です。加算器は、算術操作を使用してキャッシュ内のデータの位置を決定するために、マルチレベルのキャッシュシステムに特定のマッピング手法を実装する際にも重要です。

技術的には、アダーは、並列、シリアル、パイプラインアダーを含むさまざまな回路設計を通じて実装されます。並列加算器は、複数の数字を同時に処理する能力に好まれているため、迅速な計算を必要とするシナリオに適しています。一方、シリアル加算器は、クロックサイクルごとに1ビットを処理し、リソース制限または低電力環境に最適です。パイプラインアダーは、追加プロセスをいくつかの段階に分割し、それぞれが追加操作の一部を処理します。この設計は、特に高性能コンピューティング環境で、計算速度を大幅に向上させます。

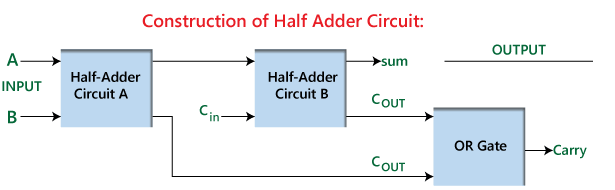

ハーフアダー回路は、デジタルエレクトロニクスの基本的なビルディングブロックであり、2つの単一のバイナリ数字を追加するように特別に設計されています。この回路は、完全な加算器の基礎を形成し、より複雑なロジック回路設計を理解するための鍵です。半分の加算器には、AとBというラベルが付いた2つの主要な入力があり、それぞれAugendとaddendを表します。このセットアップにより、以前の計算からのキャリー入力を必要とせずに、合計を計算して出力を運ぶことができます。

ハーフアダーのコアは、2つのロジックゲートで構成されています:XORゲートとアンドゲート。XORゲートは、合計出力を生成する責任があります。入力の1つだけが1である場合、1を出力する単純なルールの下で動作します。それ以外の場合は、0とゲートが出力されます。一方、ゲートは、キャリー出力を処理します。両方の入力が1の場合にのみ1を生成し、バイナリ添加の基本要件と完全に整合します。

図2:ハーフ加算器の構造

この効率的で簡単なデザインにより、ハーフアドダーは基本的なバイナリ追加を個別に実行するだけでなく、完全な加算器を作成するためのビルディングブロックとしても機能します。2つのハーフ加算器と追加またはゲートを組み合わせることにより、完全な加算器が構築されます。このセットアップでは、前半のAdderが最初の追加タスクを引き受け、予備的な合計とキャリーを生成します。その後、後半の加算器は、キャリーを追加のキャリー入力とともに処理します。最後に、ORゲートは2つのキャリー出力をマージして、最終的なキャリー出力を生成します。この配置により、加算器の機能が向上し、より複雑なマルチビット追加タスクを処理できるようになり、デジタルサーキットデザインにおけるハーフアドラーの広範なアプリケーションと重要性が示されます。

完全な加算器は、デジタルロジックデザインの高度なコンポーネントであり、一般にA、B、およびキャリーイン(CIN)としてラベル付けされた3つの単一ビットバイナリ入力の追加を処理するために装備されています。この設計により、完全な加算器は、以前の低次計算からキャリーを単一の操作に組み込むことにより、複雑なバイナリの追加を効率的に処理できます。

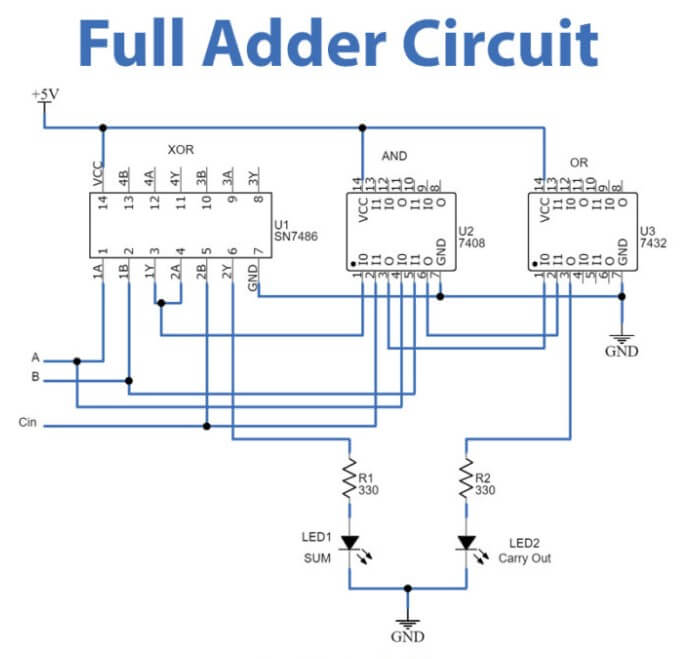

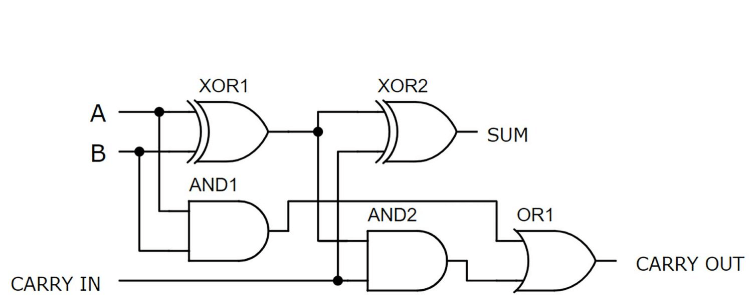

図3:フル加算回路

機能的には、完全な加算器は2桁の合計を出力できます。つまり、その出力は0〜3の範囲であり、キャリーアウト(cout)を生成することもできます。これは、すべての入力ビットが1(a = 1、b = 1、cin = 1)に設定されている場合、合計出力が1(バイナリ01を表す)になり、1のキャリーアウトが生成され、生成されるため、追加のキャリーを次のビットに渡す必要があります。

構造的には、完全な加算器は通常、2つのハーフ加算器と1つまたはゲートで構成されています。前半の加算器は入力AとBを取得し、初期合計とキャリー信号を生成します。この初期和は、キャリーイン(CIN)とともに、2番目の半分を供給します。後半のAdderの役割は、前半のAdderからCinにこの合計を追加し、別の合計と新しい侵入を生成することです。同時に、前半の加算器からのキャリー出力と後半の加算器からのキャリー出力は、またはゲートを介してマージされ、フル加算器の最終的なキャリーアウト(cout)で頂点に達します。この構造の設計により、完全な加算器が操作に加えてキャリアの伝播を効果的に処理し、マルチビットのバイナリの追加を実行するのに理想的であることが保証されます。したがって、完全な加算器の設計は、データ処理を高速化し、効率を高めるだけでなく、ロジックゲートの簡単な組み合わせを介してハードウェアの実装の複雑さを簡素化し、マルチ桁の追加と算術論理ユニットに不可欠なコンポーネントとなっています。)。

|

パラメーター

|

ハーフ加算器

|

フル加算器

|

|

説明

|

ハーフ加算器は組み合わせロジックです

2つの1ビット桁を追加する回路。ハーフアダーは2つの合計を生成します

入力。

|

完全な加算器は組み合わせロジックです

3つの1ビットバイナリ番号で追加操作を実行する回路。

完全な加算器は、3つの入力とキャリー値の合計を生成します。

|

|

以前のキャリー

|

以前のキャリーは使用されていません。

|

以前のキャリーが使用されます。

|

|

入力

|

ハーフアダーには、2つの入力ビットがあります(a、

b)。

|

完全な加算器には、3つの入力ビットがあります

(A、B、cで)。

|

|

出力

|

生成された出力は2ビットサムです

2ビットの入力から持ち運びます。

|

生成された出力は2ビットサムです

3ビットの入力から持ち運びます。

|

|

使用されます

|

ハーフアダー回路は使用できません

フルアダー回路と同じ方法。

|

完全な加算器回路を所定の位置に使用できます

ハーフアダー回路の。

|

|

特徴

|

簡単で簡単に実装できます

|

完全な加算器の設計はそうではありません

ハーフアダーのようにシンプル。

|

|

論理式

|

ハーフ加算器の論理式は次のとおりです。

s =a⊕b;c = a*b。

|

完全な加算器の論理式は次のとおりです。

s =a⊕b⊕cin;c外=(a*b)+(cで*(a⊕b))。

|

|

ロジックゲート

|

1つの元門と1つのゲートで構成されています

ゲート。

|

2つの元、2つ、ゲートで構成されています。

そして1つまたはゲート。

|

|

アプリケーション

|

計算機、コンピューターで使用されています

デジタル測定デバイスなど

|

複数のビットの追加で使用されます。

デジタルプロセッサなど

|

|

代替名

|

半分の代替名前はありません

加算器。

|

完全な加算器は、リップルキャリーとしても知られています

加算器。

|

チャート

1:ハーフアダーとフル加算器の違い

完全な加算器の真理テーブルは、その運用ロジックを理解するための鍵であり、バイナリ入力の組み合わせと対応する出力との正確な関係を詳述しています。この表は、すべての潜在的な入力シナリオとその結果を示しているため、デジタルロジック回路の設計と検証に不可欠なツールとなっています。完全な加算器は、A、B、およびAキャリーイン(CIN)の3つの入力を処理します。それぞれが0または1のいずれかになります。これにより、入力の8つの組み合わせが可能になります。

これらの組み合わせのそれぞれについて、完全な加算器からの出力には、合計(合計)とキャリーアウト(cout)が含まれます。合計は、3つの入力(A、B、およびCIN)のModulo-2追加(XOR操作)です。キャリーアウトは、少なくとも2つの入力ビットが1の場合に発生します。これは、順次加算操作でキャリーオーバーを処理する完全な加算器の機能を反映しており、より高いビット計算の精度を確保します。

説明するには、すべての入力が0(a = 0、b = 0、c-in = 0)である入力シナリオを検討してください。出力合計は0であり、キャリーも0になり、管理する追加の合計がないことを示します。a = 1、b = 0、c-in = 0などの入力ビットのみが1である場合、出力合計はキャリーなしで1になり、キャリーをより高いビットに転送する必要がないことを示します。A = 1、B = 1、C-in = 0のように2つの入力ビットが1の場合、出力合計は0です(1+1はバイナリで2に等しく、Modulo-2は0になります)が、キャリー - キャリー - アウトは1で、次のビットに渡す必要があるキャリーを示しています。最も複雑なシナリオは、3つの入力ビットすべてが1(a = 1、b = 1、c-in = 1)の場合に発生します。出力合計は1であり、1のキャリーアウトがあり、キャリー管理もさらに高いビットで必要とされる可能性があることを示唆しています。

|

a

|

b

|

cで

|

s

|

c外

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

チャート2:フルアダートゥルーステーブル

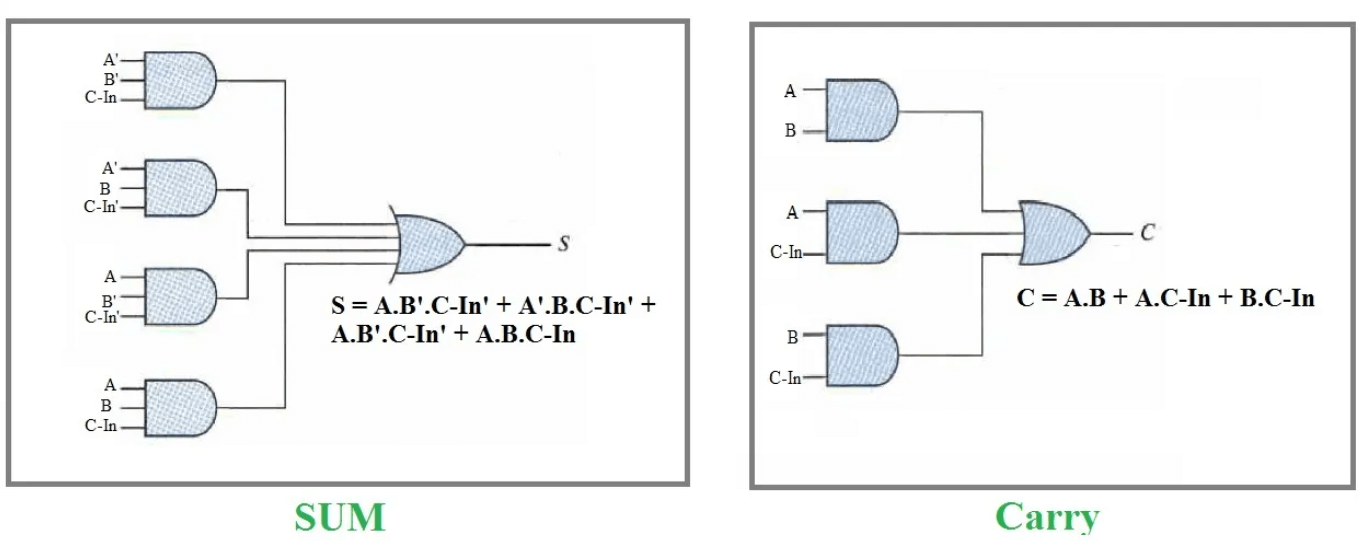

完全な加算器を理解するには、真理テーブルを使用して機能を分析することが含まれます。このテーブルでは、入力値a、b、c-inの異なる組み合わせが出力の合計とcoutにつながります。操作を把握するために、ロジック方程式を段階的に簡素化します。

合計のロジック式

方程式は、合計が1に等しい別個の場合から始まります。

•a 'b' cin + a 'b cin' + a b 'cin' + ab cin

この方程式は、CINの有無にかかわらず、用語をグループ化することで凝縮できます。

•cin(a 'b' + ab) + cin '(' b + a b ')

この単純化は、実装しやすいフォームにつながります。

•cin xor(a xor b)

この表現は、合計出力が基本的にA、B、およびCINの間のXOR操作であることを示しており、バイナリ加算のコア挙動をキャプチャします。

coutのロジック

キャリーが生成される条件から始めてください。

•a 'b cin + a b' cin + ab c-in ' + ab cin

方程式を簡素化すると、一般的にキャリーの生成を伴う用語を識別します。

•ab + b cin + a cin

カウトを実装する別の方法を探して、方程式を再編成できます。

•ab + a cin + b c-in(a + a ')

これにより、少なくとも2つの入力が1であるすべてのシナリオをキャプチャするために拡張され、組み合わせます。

•ab cin + ab + a c-in + a 'b cin

•ab(1 + cin) + a c-in + a 'b cin

•ab + a c-in(b + b ') + a' b cin

•ab + a b 'cin + a' b cin

•ab + cin(a 'b + a b')

Coutの最終的なコンパクトフォーム:

•ab + cin(a xor b)

キャリーアウト方程式のこのバージョンは、AとBの両方が1の場合、またはAまたはBの1つが持ち帰りである場合のカウトがどのように生成されるかを示しています。ビットバイナリ追加。この合理化されたロジックは、効率的なデジタル回路を実装するのに特に役立ちます。

図4:完全な加算器の方程式

完全な加算回路を実装するには、2つのハーフ加算器とORゲートを慎重に組み立てて、3つの単一ビットバイナリ入力の追加を効率的に処理できるデバイスを作成します。この配置は、回路の複雑さを最適化し、効率的かつ正確な計算の両方を保証します。

開始するために、前半の加算器は2つの主要なバイナリ入力AとBを採用します。これは、追加するメインの数字です。その重要なタスクは、これら2つの数値の合計と初期キャリーを計算することです。ここで、前半の加算器は、初期合計(SUM1)と初期キャリー(Carry1)の2つの結果を提供します。SUM1は、AとBのXOR操作から派生しており、合計に1の奇数の数があるかどうかを示します。AとBの間の操作の結果であるCarry1は、両方の数字が1であるかどうかを示し、次のビットまでキャリーを必要とする必要があります。

次に、後半の加算器がプロセスに参加します。Sum出力Sum1と3番目の入力Cin(以前の計算からの持ち込み)を入力として使用します。後半の加算器は、最終合計結果(SUM2)とセカンダリキャリー(Carry2)の2つの出力を生成します。SUM1とCINのXOR結果であるSUM2は、3つの入力の最終合計を表し、凝集したバイナリ添加を表示します。sum1とcinの間でand操作から出現するcarry2は、これらのコンポーネントによって生成されたキャリーを示します。

図5:2つのハーフ加算器を使用した完全な加算器回路

最後に、Adderの完全なデザインを完了するには、両方のハーフ加算器からCarry Outputs Carry1とCarry2を処理するためにANまたはGATEが必要です。これまたはゲートにより、計算中に生成されたキャリーが最終出力に正しく転送されることが保証されます。したがって、完全な加算器の最終的なキャリー出力(cout)は、Carrie1およびCarry2の結果または結果です。これまたはゲートを含めると、すべての潜在的なキャリーが正確に計算され、マルチビット添加操作で次のレベルに伝達されることが保証され、複数のビットにわたる算術操作の完全性が保証されます。

完全な加算器は、デジタルロジック設計に不可欠な役割を果たし、さまざまなコンピューティングやデータ処理シナリオに不可欠な多くの利点を提供します。それらの主な利点には、顕著な柔軟性、迅速な処理速度、効率的なキャリー管理が含まれます。これらの特性により、特にシーケンシャルマルチビットの追加が必要なアプリケーションで、複雑な算術操作とロジック関数を実行するのに最適なフル加算器が理想的です。

利点

柔軟性:完全な加算器は、複数のバイナリ入力(A、B、およびCIN)を同時に処理する機能に優れています。また、より長いバイナリ番号を処理するために、より大きな加算器アレイに拡張することもできます。このスケーラビリティは、複雑なマルチビット算術およびロジック操作を実行する必要がある高性能算術ロジック単位(ALU)を構築するために重要です。

速度:内部並列処理アーキテクチャのおかげで、フル加算器は、単一のクロックサイクルですべての入力の追加を完了し、出力を運ぶことも決定できます。この機能は、継続的な追加操作をサポートし、最新のマイクロプロセッサと高速コンピューティングデバイスのリアルタイムデータ処理に不可欠です。

短所

ただし、完全な加算器にも顕著な欠点があります。

設計と実装の複雑さ:フル加算器には、複数のロジックゲートとマルチレベルのキャリー伝播が含まれ、設計が複雑になります。この複雑さは、製造コストを増加させるだけでなく、回路の信頼性にも影響を与える可能性があります。

伝播遅延問題:伝播の伝播は、それぞれが遅延を追加するいくつかのロジックゲートを通過する場合があります。これにより、特に大規模なコンピューターシステムで、および非常に大規模なスケール統合(VLSI)および高速プロセッサの設計で、大規模な操作中の全体的な計算速度が制限されます。遅延は、パフォーマンスの重要なボトルネックになる可能性があります。

これらの問題を軽減するために、エンジニアはより効率的な回路設計を継続的に調査します。戦略には、より高速のロジックゲートテクノロジーの使用、回路レイアウトを最適化してパスの長さを短縮すること、キャリーゼアーダーなどの高度なテクノロジーを開発して、キャリー伝播の遅延を最小限に抑えることが含まれます。

完全な加算器は、デジタルロジックで広く使用されており、柔軟性と効率性が高く評価されており、多数のコンピューティングおよびデータ処理タスクの中心になっています。それらのアプリケーションは、基本的な算術操作から複雑な信号処理とシステム制御に及びます。フル加算器が不可欠ないくつかの重要な領域を詳細に見てみましょう。

算術回路

フル加算器の最も簡単な用途の1つは、バイナリ追加を実行する算術回路にあります。特にマルチビット数の追加において非常に重要なフル加算器は、カスケードを通じてより長いバイナリシーケンスを管理します。この配置では、それぞれのフル加算器がビット位置とキャリーを下位ビットからのキャリーの追加を処理し、次に新しいキャリーを次の高ビットのフル加算器に渡します。このカスケードにより、桁全体にわたって包括的なマルチビットの追加が可能になります。

情報処理

完全な加算器は、フィルタリングやフーリエ変換用のデジタル信号処理(DSP)などの高度なデータ処理タスクでも極めて重要な役割を果たします。さらに、データ暗号化とエラー検出、パリティチェックや周期冗長チェック(CRC)コード生成などの修正アルゴリズムなど、情報セキュリティの領域では、必須ビット操作を実行するためにフル加算器が重要です。

カウンター

デジタルカウンターでは、特にモジュラーカウンターと同期カウンターで、増分関数と減少関数の両方を実装するために、完全な加算器が不可欠です。キャリーと借用を正確に管理して、正確なカウントを確保します。

マルチプレクサ(MUX)とDemultiplexers(Demux)

マルチプレクサとDemultiplexersでは、フル加算器がチャネル選択とデータ分布に重要な役割を果たします。彼らは、データ入力と出力に使用されるチャネルを決定するロジックに参加し、ロジック制御信号に基づいて決定を下します。

メモリテクノロジー

メモリアドレス指定では、フル加算器がメモリの位置に動的にアクセスするためのアドレス信号を生成するのに役立ちます。これは、動的ランダムアクセスメモリ(DRAM)およびその他のストレージシステムで特に重要です。フル加算器は、メモリアクセスの効率を高めるための複雑なアドレス計算をサポートします。

算術論理単位(ALU)

最後に、マイクロプロセッサおよびデジタル信号プロセッサの算術論理単位の基本的なコンポーネントとして、完全な加算器が重要です。ALUはすべての算術操作とロジック操作を処理し、完全な加算器がデータが迅速かつ正確に処理されることを保証します。

さまざまなロジックゲートと構成を使用して、完全な加算器を構築できます。ここでは、4つの異なる実装を検討し、セットアップと運用上のニュアンスを強調します。

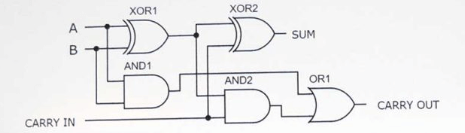

Xorで構築された完全な加算器、および、またはゲート

図6:XORで構築された完全な加算器、および、またはロジックゲート

この例では、個別のトランジスタを使用してブレッドボードの上に構築された完全な加算器を紹介します。構成には、5つのロジックゲートが含まれます。2つのXorゲート、2つとゲート、1つまたはゲートで、合計21のトランジスタが必要です。入力AとBは、ブレッドボードの左上に接続されており、A +5V電源が受けられます。これらの入力は、2つのトグルスイッチを使用して制御されます。左上にある2つのLEDは、入力AとBの状態を示し、右側の2つのLEDが出力を表示します。回路で使用される抵抗器はすべて2.2kオームです。入力aとbがオンであり、持ち帰りがオフになると、出力は10のバイナリ値を示し、合計2(1 + 1 + 0 = 10)を表します。最初の12個のトランジスタで構築されたXorゲートは、一次合計を処理し、ブレッドボードの下半分にはキャリー操作用のおよびまたはゲートが含まれているため、色分けされた配線は明瞭さとトラブルシューティングを強化します。

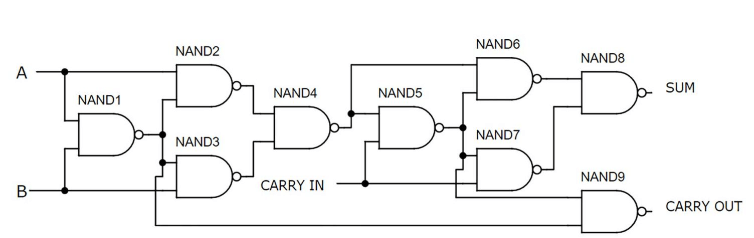

NANDゲートを使用した完全な加算器

図7:Nand Gatesを使用した完全な加算器

この完全な加算器は9つのナンドゲートを利用し、各ゲートは2つのトランジスタで作られ、合計18のトランジスタがあります。この方法は、離散コンポーネントを使用して完全な加算器を構築する最も簡単で効率的な方法の1つです。すべてのゲートはブレッドボードの上半分に組み立てられ、スイッチは下半分を占有します。回路の機能は、入力AおよびBオン、およびキャリースオフで実証され、10進数に相当する出力バイナリ値が10になります。

Nor Gatesを備えた完全な加算器

図8:NORゲートを含む完全な加算器

9つのゲートで構成されており、それぞれが2つのトランジスタを必要とするこのセットアップでは、合計18のトランジスタも使用しています。NOR Gatesで完全な加算器を構築することは、優れた代替手段を提供しますが、NANDゲートと比較してより複雑な配線が含まれます。NORゲートの各トランジスタは接地されており、コレクターはオレンジジャンパーワイヤで接続され、きちんとした整理された配線を確保しています。この構成は、入力AとBがアクティブ化され、キャリーインが無効になっていることで表示され、キャリーがアクティブで合計がオフになっている出力につながります。

基本的なハーフ加算器から洗練されたフル加算器デザインまで、このアダーテクノロジーの探索を通して、これらのコンポーネントがデジタルエレクトロニクスの進歩に基づいていることが明らかです。提供された運用の特性と実装の例は、さまざまな計算設定での加算器の汎用性と効率を強調しています。特にそれらの真理テーブルと特性方程式を通じて、加算器の構造と機能を調べることにより、それらの能力と制約に対する貴重な洞察を得ます。この知識は、より効率的で高速なコンピューティングシステムの設計を進めるのに役立ちます。最終的に、加算器は複雑なバイナリ計算を簡素化するだけでなく、データ処理、メモリ割り当て、デジタル信号処理などの多様な分野でのテクノロジーの急増を可能にします。デジタルテクノロジーが進化するにつれて、Adder設計の継続的な洗練と革新は、より高度な計算アーキテクチャの開発の基礎となり続け、これらの基本的なコンポーネントがデジタルシステムの設計と実装の中心に留まることを保証します。

よくある質問[FAQ]

1.フル加算回路とは何ですか?

完全な加算器は、3つのバイナリビットを追加して合計と侵入出力を生成するデジタル回路です。これは、3つの入力の追加を処理するように設計されています。2つの重要なビットと1つの持ち込みビット以前の追加から。これにより、マルチビットのバイナリ番号を追加するために、連続した段階で使用できます。

2.フル加算器のXORはいくつですか?

典型的なフル加算器が含まれています:

合計を生成するための2つのXORゲート。

キャリーアウトの計算に貢献する2つのゲート。

キャリーアウト出力を完成させるための1つまたはゲート。

3.フル加算器のキャリー入力とは何ですか?

完全な加算器のキャリー入力(CIN)は、マルチビットバイナリ添加の以前の低い有意ビットの追加によるキャリービットです。現在の合計と新しいキャリーアウトを計算するときに、完全な加算器がこの以前のキャリーを考慮することができます。

4.半分の加算器の代わりにフル加算器を使用するのはなぜですか?

3ビット(以前の追加からのキャリーを含む)を追加できるため、半分の加算器の代わりに完全な加算器が使用され、マルチビット数を追加するために一緒にチェーンを接続するのに適しています。ハーフアダーは2ビットしか追加できず、持ち込みのための準備がありません。これにより、その使用は、シーケンシャルキャリー伝播なしで最も単純な形式のバイナリ加算に制限されます。