信号処理のAD9959機能の理解

AD9959は、4つの独立したチャネルで周波数、位相、振幅を制御する強力で柔軟なデジタルシンセサイザーです。この記事では、AD9959の主要な機能、技術仕様、および一般的なアプリケーションについて説明しているため、このデバイスをさまざまなセットアップで使用する方法を理解しやすくなります。アジャイルローカルオシレーターを作成したり、フェーズドアレイレーダーなどの複雑なシステムを同期したい場合でも、AD9959は幅広いプロジェクトに必要な精度と適応性を提供します。このガイドの終わりまでに、AD9959がどのように機能するか、さまざまなフィールドでどのように適用できるかを明確に理解することができます。カタログ

AD9959の概要

AD9959 4つの直接的なデジタルシンセサイザーコアを提供するため、各チャネルの周波数、位相、振幅を個別に制御できます。周波数、位相、または振幅であろうと、最大16レベルの変調を処理する機能により、設計に柔軟性をもたらします。すべてのチャネルが同じシステムクロックを共有するため、それらは同期したままで、複数のチャネルでスムーズな動作を確保します。さらに、複数のAD9959を使用している場合は、複数のデバイスを簡単に同期できるため、複雑なセットアップに最適です。

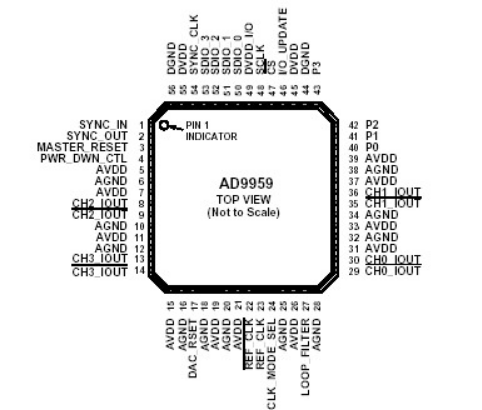

AD9959ピンアウト図

| ピン番号 | ニモニック | I/o | 説明 |

| 1 | sync_in | 私 | 複数のAD9959デバイスを同期するために使用されます。Master AD9959デバイスのSync_out Pinに接続します。 |

| 2 | sync_out | o | 複数のAD9959デバイスを同期するために使用されます。スレーブAD9959デバイスのsync_inピンに接続します。 |

| 3 | master_reset | 私 | アクティブな高リセットピン。Master_resetピンをアサートすると、AD9959内部レジスタがデフォルトの状態になります。 |

| 4 | PWR_DWN_CTL | 私 | 外部電源制御。 |

| 5、7、11、15、19、21、26、31、33、37、39 | AVDD | 私 | アナログ電源ピン(1.8V)。 |

| 6、10、12、16、18、20、25、28、32、34、38 | agnd | 私 | アナロググランドピン。 |

| 44、56 | DVDD | 私 | デジタル電源ピン(1.8V)。 |

| 45、55 | DGND | 私 | デジタルパワーグラウンドピン。 |

| 8 | Ch2_iout | o | 真のDAC出力。AVDDに終了します。 |

| 9 | Ch2_iout | o | 相補的なDAC出力。AVDDに終了します。 |

| 13 | Ch3_iout | o | 真のDAC出力。AVDDに終了します。 |

| 14 | Ch3_iout | o | 相補的なDAC出力。AVDDに終了します。 |

| 17 | DAC_RSET | 私 | すべてのDACの参照電流を確立します。1.91kΩ抵抗(名目)は、ピン17からAGNDに接続されています。 |

| 22 | ref_clk | 私 | 相補的な参照クロック/発振器入力。REF_CLKがシングルエンドモードで動作している場合、このピンは0.1 µFコンデンサを使用してAVDDまたはAGNDに分離する必要があります。 |

| 23 | ref_clk | 私 | 参照クロック/発振器入力。REF_CLKがシングルエンドモードで動作している場合、これは入力です。参照クロック構成については、操作モードセクションを参照してください。 |

| ピン番号 | ニモニック | I/o | 説明 |

| 24 | clk_mode_sel | 私 | 発振器セクションのコントロールピン。注意:このピンを1.8Vを超えて運転しないでください。High(1.8V)の場合、発振器セクションがREF_CLKソースとしてクリスタルを受け入れることができます。低い場合、発振器セクションがバイパスされます。 |

| 27 | loop_filter | 私 | PLLループフィルターの外部ゼロ補償ネットワークに接続します。通常、ネットワークは、AVDDに結ばれた680pfコンデンサを備えた直列の0Ω抵抗で構成されています。 |

| 29 | ch0_iout | o | 相補的なDAC出力。AVDDに終了します。 |

| 30 | ch0_iout | o | 真のDAC出力。AVDDに終了します。 |

| 35 | ch1_iout | o | 相補的なDAC出力。AVDDに終了します。 |

| 36 | ch1_iout | o | 真のDAC出力。AVDDに終了します。 |

| 40〜43 | P0からP3 | 私 | 変調に使用されるデータピン(FSK、PSK、ASK)、スイープアキュムレーターを起動/停止するか、出力の振幅を上昇/ランプするために使用します。データは、sync_clk(ピン54)と同期しています。データ入力は、sync_clkのセットアップを満たし、時間要件を保持する必要があります。これらのピンの機能は、プロファイルピン構成(PPC)ビット(FR1 [14:12])によって制御されます。 |

| 46 | i/o_update | 私 | ライジングエッジは、シリアルI/Oポートバッファーからアクティブレジスタにデータを転送します。I/O_UPDATEはSYNC_CLK(ピン54)と同期しています。I/O_UPDATEは、DAC出力へのデータの固定パイプライン遅延を保証するために、Sync_CLKのセットアップと時間要件を満たし、保持する必要があります。それ以外の場合は、±1パイプラインの不確実性の±1 sync_clk期間が存在します。最小パルス幅は1つのSync_Clk期間です。 |

| 47 | cs \ | 私 | アクティブな低チップ選択。複数のデバイスが一般的なI/Oバス(SPI)を共有できるようにします。 |

| 48 | sclk | 私 | I/O操作のシリアルデータクロック。データビットはSCLKの立ち上がりエッジに書かれており、SCLKの下向きの端で読み取られます。 |

| 49 | dvdd_i/o | 私 | SPIポートおよびデジタルI/O用の3.3Vデジタル電源。 |

| 50 | SDIO_0 | I/o | データピンSDIO_0は、シリアルポートI/Oのみに専用です。 |

| 51、52 | SDIO_1、SDIO_2 | I/o | データピンSDIO_1およびデータピンSDIO_2は、シリアルI/Oポートに使用するか、DAC出力振幅のランプアップ/ランプダウン(RU/RD)を開始するために使用できます。 |

| 53 | SDIO_3 | I/o | データピンSDIO_3は、シリアルI/Oポートに使用するか、DAC出力振幅のランプアップ/ランプダウン(RU/RD)を開始できます。単一ビットモードまたは2ビットモードでは、SDIO_3がsync_i/oに使用されます。sync_i/o関数が使用されていない場合は、それを接地またはロジックに結び付けます。sdio_3を単一ビットまたは2ビットモードにフロートさせないでください。 |

| 54 | sync_clk | o | sync_clkは、システムクロックレートの4分の1で実行されます。無効にすることができます。I/O_UPDATEまたはデータ(ピン40からピン43)は、同期して同期します。DAC出力へのデータの固定パイプライン遅延を保証するには、I/O_UPDATEまたはデータ(ピン40からピン43)がセットアップの要件を満たし、SYNC_CLKの立ち上がりエッジへの時間要件を保持する必要があります。それ以外の場合、±1 sync_clk不確実性の期間が発生します。 |

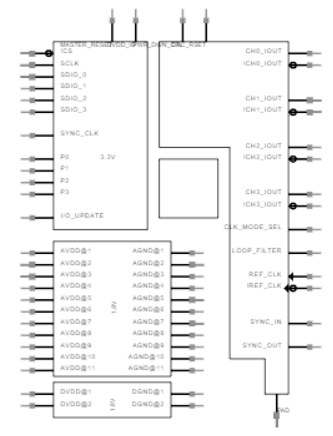

AD9959 CADモデルの概要

AD9959シンボル

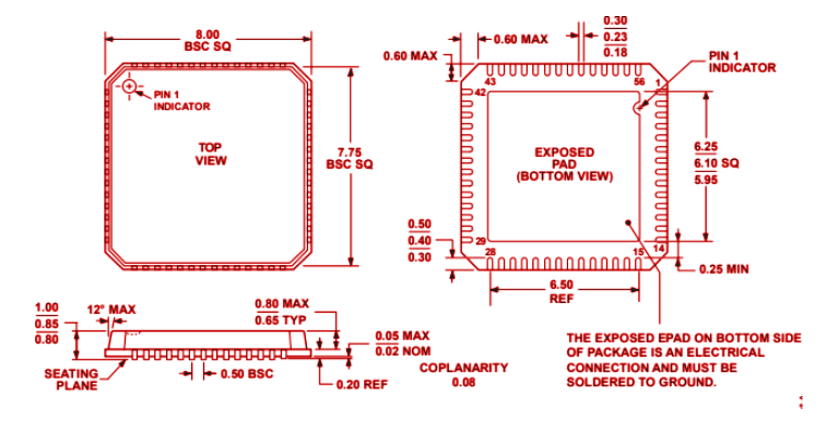

AD9959フットプリント

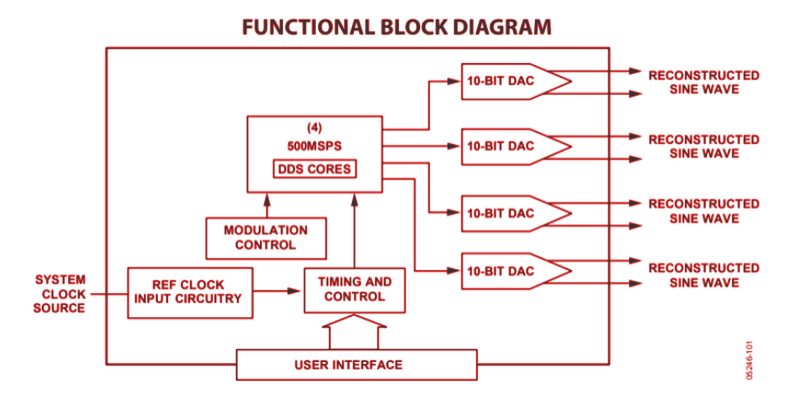

詳細なAD9959ブロック図

AD9959技術仕様

Analog Devices Inc. AD9959BCPZの技術仕様、属性、パラメーター、および同等の部品。

| タイプ | パラメーター |

| ライフサイクルステータス | |

| 工場のリードタイム | 8週間 |

| めっきに連絡してください | 錫 |

| マウント | 表面マウント |

| 取り付けタイプ | 表面マウント |

| パッケージ /ケース | 56-VFQFN露出パッド、CSP |

| ピンの数 | 56 |

| 動作温度 | -40°C〜85°C |

| パッケージング | トレイ |

| JESD-609コード | E3 |

| pbfreeコード | いいえ |

| パーツステータス | アクティブ |

| 水分感度レベル(MSL) | 3(168時間) |

| 終端の数 | 56 |

| 終了 | SMD/SMT |

| ECCNコード | ear99 |

| 追加機能 | また、3.3Vの供給が必要です |

| 最大電力散逸 | 680MW |

| 電圧 - 供給 | 1.71V〜1.96V |

| 端子位置 | クワッド |

| 端子形式 | リードなし |

| ピークリフロー温度(°C) | 260 |

| 供給電圧 | 1.8V |

| 端子ピッチ | 0.5mm |

| 頻度 | 500MHz |

| time @ peakリフロー温度(s) | 30 |

| ベースパーツ番号 | AD9959 |

| ピンカウント | 56 |

| 資格ステータス | 資格がない |

| 動作電源電圧 | 1.8V |

| インタフェース | シリアル |

| 供給電流の動作 | 180ma |

| 公称供給電流 | 160ma |

| 最大供給電流 | 185ma |

| UPS/UCS/末梢ICタイプ | |

| ビット数 | 10 |

| サンプリングレート | 500 MSP |

| 境界スキャン | いいえ |

| ローパワーモード | はい |

| 変換率 | 500 MSP |

| D/Aコンバーターの数 | 4 |

| 解像度(ビット) | 10 b |

| チューニングワード幅(ビット) | 32 b |

| 身長 | 830μm |

| 長さ | 8mm |

| 幅 | 8mm |

| SVHCに到達します | SVHCなし |

| ROHSステータス | ROHS3準拠 |

| 鉛フリー | リードが含まれています |

AD9959キー機能

500 MSPで4つの同期DDSチャネル

AD9959は、4つの同期されたダイレクトシンセサイザー(DDS)チャネルを提供し、すべて最大500 MSPで動作します。これにより、同期を維持しながら複数のチャネルにわたって正確な信号を生成できます。これは、複数の出力をスムーズに連携する必要があるプロジェクトに取り組む場合に特に役立ちます。

独立した周波数、位相、および振幅制御

4つのDDSチャネルのそれぞれは、周波数、位相、および振幅を独立した制御を提供します。これにより、さまざまなニーズに合わせて各チャネルを微調整できるため、さまざまな信号パラメーターの処理に柔軟に対応できます。

周波数、位相、および振幅の変化について一致したレイテンシー

AD9959は、周波数、位相、振幅の変化がチャネル間で同期されることを保証します。これは、1つのパラメーターを調整すると、すべてのチャネルで変更が同時に行われ、遅延なしで一貫した出力を維持するのに役立つことを意味します。

優れたチャネルからチャネルへの分離

AD9959は、65 dBを超えるチャネル間分離により、チャネル間の干渉を最小限に抑えます。これにより、各チャネルで生成された信号がクリーンで明確であることが保証され、デザインでより高い品質のパフォーマンスが提供されます。

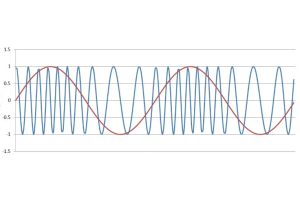

線形掃引機能

AD9959は、線形周波数、位相、および振幅スイープをサポートします。この機能により、値間のスムーズな移行が可能になり、時間の経過とともに徐々に変化する信号を簡単に生成できます。これは、テストとキャリブレーションの目的に役立ちます。

周波数、位相、および振幅変調の最大16レベル

このデバイスは、周波数、位相、または振幅の最大16レベルの変調を処理できます。このレベルの柔軟性により、プロジェクトのニーズに応じて、シンプルから複雑なものまで、さまざまな変調スキームを実装できます。

統合された10ビットデジタルからアナログコンバーター(DACS)

各チャネルには、独自の統合された10ビットDACが付属しているため、デジタル信号を精度でアナログ出力に変換できます。これにより、AD9959は、コンパクトな形で正確なアナログ信号生成が必要な場合に最適です。

個別にプログラム可能なDACフルスケール電流

各DACのフルスケール電流を個別にプログラムできます。これにより、各チャネルの出力電力を制御できます。このレベルのカスタマイズを使用すると、特定の要件に基づいてさまざまなチャネルのパワーレベルを最適化できます。

細かい周波数チューニング解像度

AD9959は0.12 Hz以上のチューニング解像度を提供し、生成する信号の周波数を正確に制御します。このレベルの精度は、小さな周波数調整が大きな違いをもたらすアプリケーションで作業する場合に有益です。

高解像度の位相オフセット

14ビットの位相オフセット解像度により、AD9959を使用すると、各チャネルの位相を微調整できます。この機能は、フェーズドアレイシステムで複数の信号を整列する場合など、信号間で正確な位相調整が必要な場合に役立ちます。

出力振幅スケーリング

AD9959は、10ビット出力振幅スケーリング解像度を提供します。これにより、出力振幅を高精度で調整することができ、信号強度をより正確に制御する柔軟性が得られます。

強化されたシリアルI/Oポートインターフェイス

シリアルI/Oポートインターフェイス(SPI)は、拡張されたデータスループットを提供し、デバイスとシステム間でデータを迅速かつ効率的に転送できるようにします。これにより、通信が高速化されます。これは、ペースの速いアプリケーションで役立ちます。

パワーダウンコントロール

AD9959には、電源を入れるためのソフトウェアとハードウェアの両方のオプションが含まれており、電源を節約する方法と時期を制御できます。この機能は、電力効率が優先事項であるエネルギー志向の設計で特に役立ちます。

二重供給操作

デバイスは、DDSコアで1.8 V、シリアルI/Oで3.3 Vで動作します。この構成は、パフォーマンスと電力ニーズのバランスをとるのに役立ち、さまざまな設計環境に適応できます。

複数のデバイスの同期

AD9959は複数のデバイスでの同期をサポートしているため、それらの間の正確なタイミングを維持しながら、追加のユニットでデザインを拡張できます。これにより、同期を失うことなくプロジェクトを簡単に拡大できます。

選択可能なrefclk乗数

AD9959は、4x〜20xの範囲の選択可能なRefCLK乗数を使用して、クロッキングオプションの柔軟性を提供し、デザインに最適な設定を選択できます。

内蔵refclkクリスタルオシレーター

このデバイスには、外部コンポーネントの必要性を削減することで設計プロセスを簡素化し、システム内のタイミングを簡単に管理できるようにするために、設計プロセスを簡素化する組み込みのRefCLKクリスタルオシレーターが含まれています。

コンパクト56リードLFCSPパッケージ

AD9959には56リードLFCSPパッケージがあり、複数のDDSチャネルを設計に統合するためのコンパクトでスペース節約オプションを提供します。この小さなフォームファクターは、ボードスペースがあまりにも多くなくても高い機能を必要とする場合に理想的です。

一般的なAD9959アプリケーション

アジャイルローカルオシレーター

AD9959は、アジャイルローカル発振器での使用に適しており、周波数、位相、および振幅を正確に制御できます。これにより、無線システムまたは他の通信機器で柔軟で調整可能な信号生成が必要な場合に最適なオプションになります。

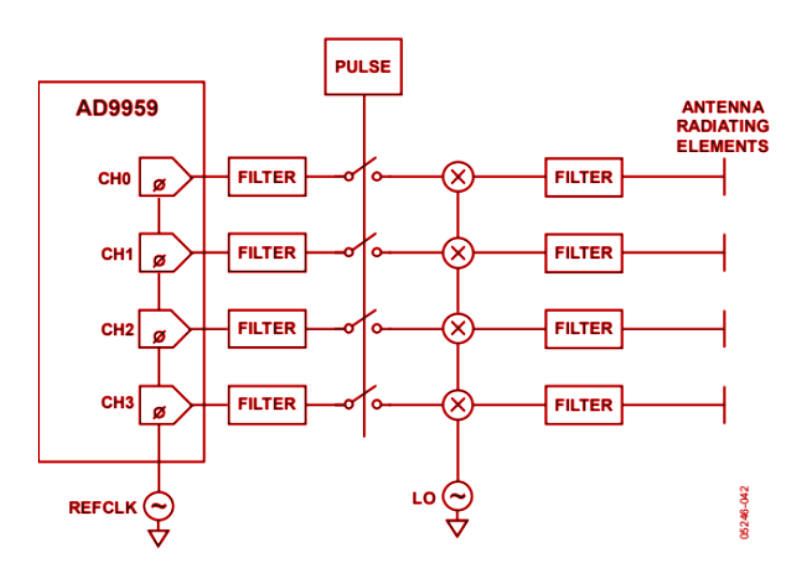

段階的なアレイレーダーとソナー

フェーズドアレイレーダーおよびソナーシステムでは、複数の信号チャネルの正確な同期が重要です。AD9959が複数のチャネルにわたって独立した制御と同期を処理する機能により、これらのアプリケーションにぴったりで、正確な信号処理とタイミングが確保されます。

計装

AD9959は、さまざまなタイプの機器、特に正確な信号生成と制御を必要とするデバイスで使用できます。テスト、測定、またはキャリブレーションシステムのいずれであっても、頻度、位相、振幅の調整におけるデバイスの柔軟性は、設計に汎用性を高めます。

同期されたクロッキング

複数のチャネルにわたって同期したクロックを必要とするプロジェクトの場合、AD9959は優れたソリューションを提供します。組み込みの同期機能により、チャネル間の正確なタイミングを維持することができ、タイミングの精度が重要なシステムに最適です。

Acoustto-optic TunableフィルターのRFソース(AOTF)

AD9959は、これらの光学システムに信頼性の高い正確な信号生成を提供する、音響光学的調整可能なフィルター(AOTF)のRFソースとして機能します。周波数と振幅制御の柔軟性により、このような専門的なアプリケーションの要求を満たすことができます。

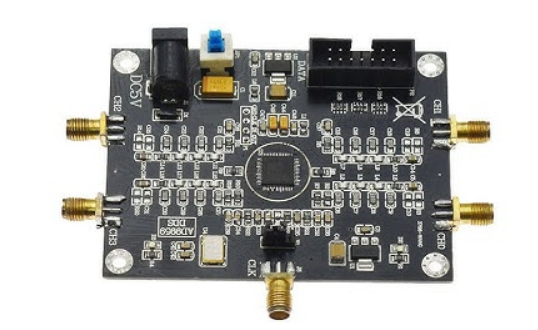

AD9959アプリケーション回路の概要

AD9959次元アウトライン図

AD9959メーカー情報

Analog Devicesは、1965年以来、統合回路の作成における大手企業です。同社は、電気信号のように、温度、音、動きなど、現実世界からの信号を変換、状態、および処理するのに役立つ回路の設計と生産を専門としています。これらの回路は、世界中の幅広い電子システムで使用されています。

よくある質問[FAQ]

1。AD9959は何に使用されていますか?

AD9959には、4つの直接的なデジタルシンセサイザー(DDS)コアが含まれており、それぞれそれぞれのチャネルでの周波数、位相、および振幅の独立した制御が可能になります。この柔軟性は、PCBのフィルタリング、増幅、レイアウトの違いなどのアナログプロセスによって引き起こされる信号の矛盾のバランスをとるのに役立ちます。

2。AD9959はどのように機能しますか?

AD9959は、最大16個の異なるレベルで周波数、位相、または振幅(FSK、PSK、またはASK変調)を変調できます。プロファイルピンに信号を適用することにより、この変調を制御します。これにより、チップは必要に応じて異なる変調レベルを切り替えることができます。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

TC7660COA電圧コンバーターの包括的なガイド

10/24/2024で公開されています

TIP120トランジスタの理解

10/24/2024で公開されています

ホットポスト

-

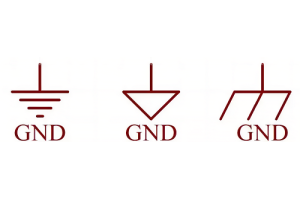

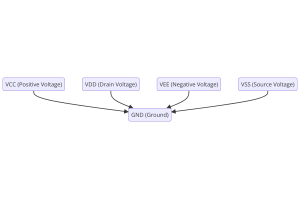

回路のGNDとは何ですか?

01/1/1970で公開されています 2924

-

RJ-45コネクタガイド:RJ-45コネクタカラーコード、配線スキーム、R-J45アプリケーション、RJ-45データシート

01/1/1970で公開されています 2484

-

ファイバーコネクタタイプ:SC対LCおよびLC対MTP

01/1/1970で公開されています 2075

-

エレクトロニクスVCC、VDD、VEE、VSS、およびGNDの電源電圧の理解

11/8/0400で公開されています 1863

-

DB9とRS232の比較

01/1/1970で公開されています 1757

-

LR44バッテリーとは何ですか?

そのユビキタスな力は、些細なガジェットから生命を脅かす医療機器まで、私たちの日常生活のあらゆる側面に静かに浸透し、静かな役割を果たします。しかし、このエネルギーを本当に把握し、特にそれを保存して効率的に出力する方法は、簡単な作業ではありません。この背景に反して、この記事は、表面上では重要ではないように見えるかもしれないが、実際の用途、つまりLR44バッテリーでは非常に用途が広いものになる可能性のあるコ...01/1/1970で公開されています 1706

-

基礎を理解する:インダクタンス抵抗、および副次的

電気工学の複雑なダンスでは、基本的な要素のトリオが中心的な舞台、つまりインダクタンス、抵抗、静電容量です。それぞれが、電子回路の動的なリズムを決定するユニークな特性を備えています。ここでは、これらのコンポーネントの複雑さを解読し、広大な電気オーケストラ内でそれらの明確な役割と実用的な使用を明らかにするための旅に着手します。インダクタンス、その磁束魔法のwizardry;抵抗、電流の流れの不動の門番;電荷のア...01/1/1970で公開されています 1649

-

CR2430バッテリー包括的なガイド:仕様、アプリケーション、およびCR2032バッテリーとの比較

CR2430バッテリーとは何ですか?CR2430バッテリーの利点規範CR2430バッテリーアプリケーションCR2430相当CR2430対CR2032バッテリーCR2430サイズCR2430と同等物を購入するときに何を探すべきかデータシートPDFよくある質問 バッテリーは小さな電子機器の中心です。利用可能な多くのタイプの中で、コイン細胞は、計算機、リモートコントロール、および時計によく見られる重要な役割を果たします。サイズが小さいにもかかわらず、各コ...01/1/1970で公開されています 1536

-

RFとは何ですか?なぜそれを使用するのですか?

無線周波数(RF)テクノロジーは、最新のワイヤレス通信の重要な部分であり、物理的な接続なしで長距離にわたってデータ伝送を可能にします。この記事では、RFの基本を掘り下げ、電磁放射(EMR)がRF通信を可能にする方法を説明します。EMRの原則、RF信号の作成と制御、およびそれらの幅広い用途を探ります。この記事では、RFテクノロジーの歴史的なマイルストーン、関係する技術的課題、および信頼できるRFコミュニケーションを確...01/1/1970で公開されています 1528

-

CR2450対CR2032:代わりにバッテリーを使用できますか?

リチウムマンガンバッテリーには、他のリチウム電池といくつかの類似点があります。高エネルギー密度と長いサービス寿命は、彼らが共通している特性です。この種のバッテリーは、独自の安全性のために多くの消費者の信頼と好意を獲得しています。高価なハイテクガジェット?私たちの家に小さな電化製品?周りを見回すと、どこにでも表示されます。これらの多くのリチウムマンガンのバッテリーの中で、CR2450バッテリーとCR2032バッ...01/1/1970で公開されています 1497