To: Valued Customer

Issue Date : 22 May 2020

Toshiba Electronic Devices & Storage Corporation System Devices Marketing Center System Devices Sales & Marketing Dept. Logic LSI & Microcomputer Group

####

Thank you for your constant support to Toshiba Products.

#### Part Number affected:

TMPM066, M3H (Group1), M3H (Group 2), M4K (Group 1), M4K (Group 2)

#### The reason of announcement:

Discovery of technical limitation for certain function related to MCU IP operation.

Technical disclosure on product function limitation condition and workaround described in attached. Final errata for affected product will be made available on-line in coming month.

For questions or concerns regarding this notification, please feel free to contact your local sales office or Customer service representative.

Sincerely yours,

To: Distributor

# <u>Product defect related to Serial Peripheral</u> Interface (TSPI) utilize DMA Controller (DMAC)

## TOSHIBA

2020/May/27

Toshiba Electronic Devices & Storage Corporation

Toshiba Electronic Device Solutions Corporation

Thank you for using Toshiba microcontrollers.

In the data transfer of DMAC + TSPI, a problem was found that some data was discarded.

This document will address the phenomenon and workaround.

We apologize for any inconvenience, but we ask that you review the content. If you have any questions about this matter, please contact our sales representative.

## Technical terms explanation

| The function     | Technical Terms                | The explanation                                                                                                                                                                                                                                                                        |

|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Related Function |                                | DMAC, APB Interface, TSPI                                                                                                                                                                                                                                                              |

| TSPI             | TSPI                           | Toshiba Serial Peripheral Interface                                                                                                                                                                                                                                                    |

|                  | FIFO                           | Transmit/Receive FIFO 8 stage (7 to 16-bit), 4 stage(17 to 32-bit)                                                                                                                                                                                                                     |

|                  | BREQ, SREQ                     | DMA Request<br>BREQ (Burst-transfer request) cab transfer multiple data with one request.<br>(Number of transfers depends on DMA settings register.)<br>SREQ (Single-transfer request) can transfer one data with one request.                                                         |

|                  | Fill level (n)                 | DMA Transmit : BREQ and SREQ are generated when FIFO level N and under.<br>SREQ will occur if there is FIFO space.                                                                                                                                                                     |

| DMAC             | DMAC                           | DMA controller                                                                                                                                                                                                                                                                         |

|                  | Arbitration                    | Arbitration interval = Number of transfer when BREQ occurs.                                                                                                                                                                                                                            |

|                  | Single-transfer is<br>disabled | DMAC can ignore SERQ when burst transfer is possible by single-transfer is disable.<br>However, if the remaining transfer count is a fraction less than the burst transfer count, single transfer is automatically enabled.                                                            |

| APB Interface    | Write-buffer                   | The bus arbitration circuit between AHB and APB bus has a single-stage write buffer.<br>The DMAC releases the AHB bus first when write to the write buffer is completed.<br>After that, DMAC writes to the APB bus.<br>* There is a time lag between DMAC and peripheral write timing. |

[Applicable products]

M3H Group(1), M3HGroup(2), M4K Group(1), M4K Group(2)

\*Detailed product names are shown in the bottom of this document.

[Configuration that occur]

Combination of DMAC + APBIF + TSPI

[Phenomenon]

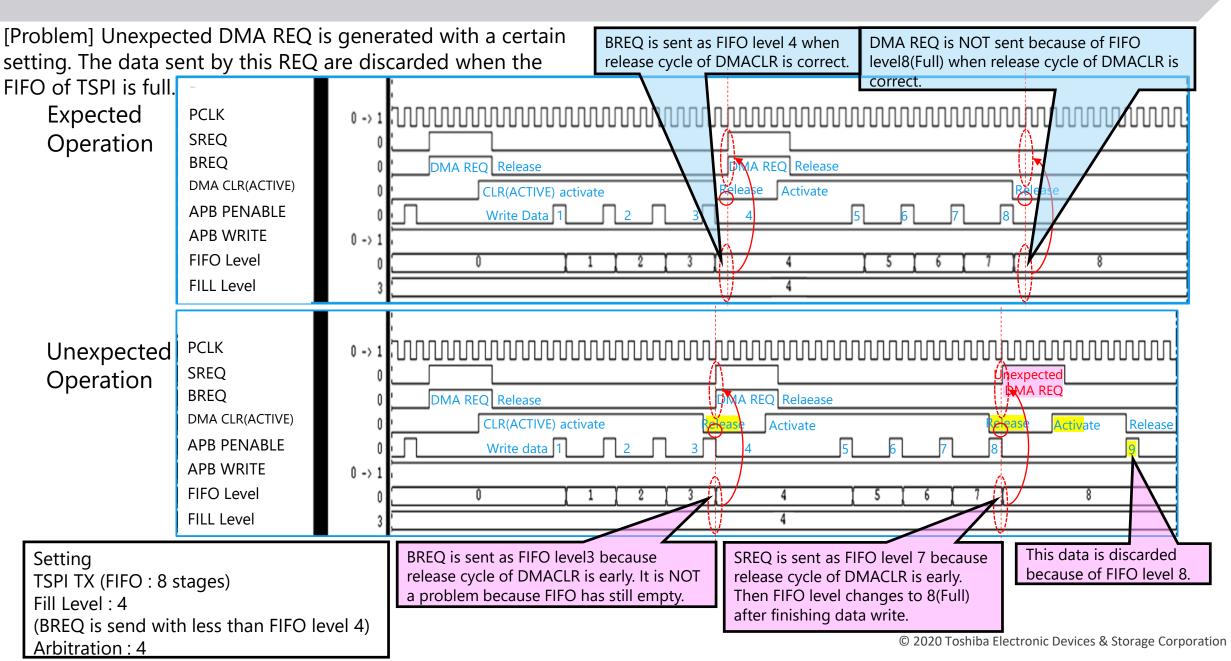

When transmitting data to TSPI using the DMAC, FIFO control may not be performed correctly depending on the DMAC and TSPI setting conditions, and the data transferred by the DMAC to the TSPI may be discarded.

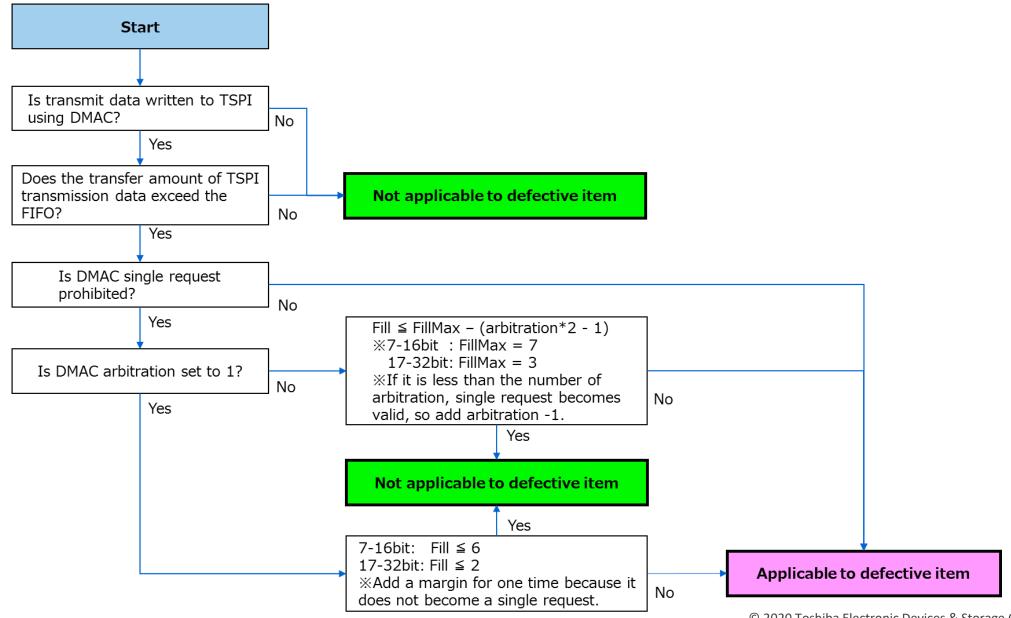

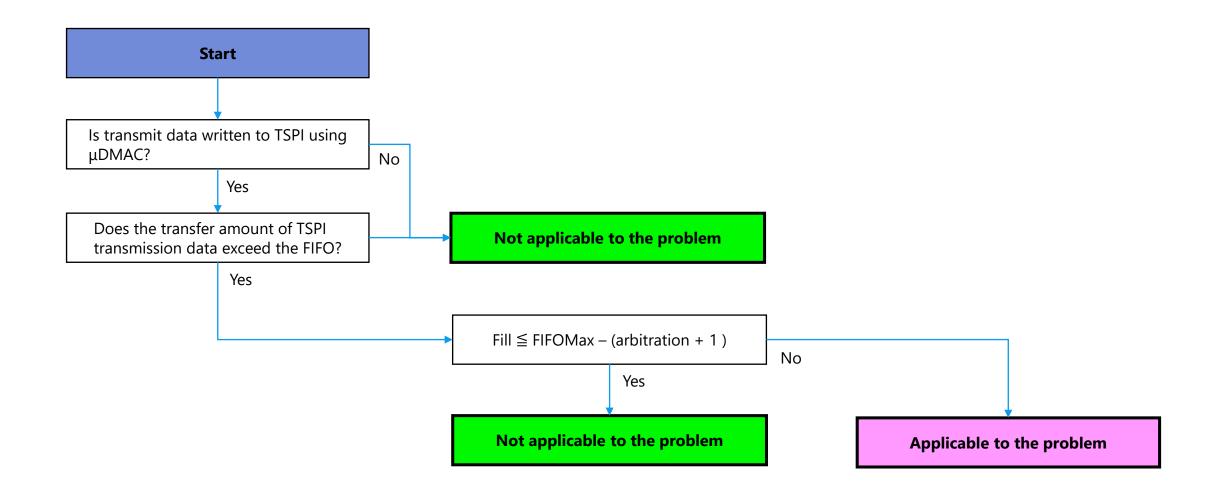

The following page shows the check flow of the occurrence conditions.

## DMAC+TSPI Check flow

© 2020 Toshiba Electronic Devices & Storage Corporation

4

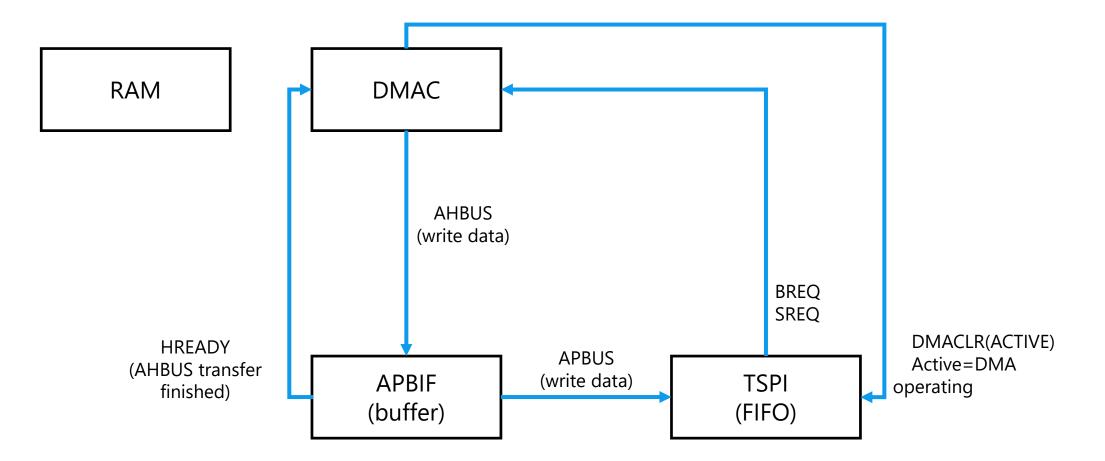

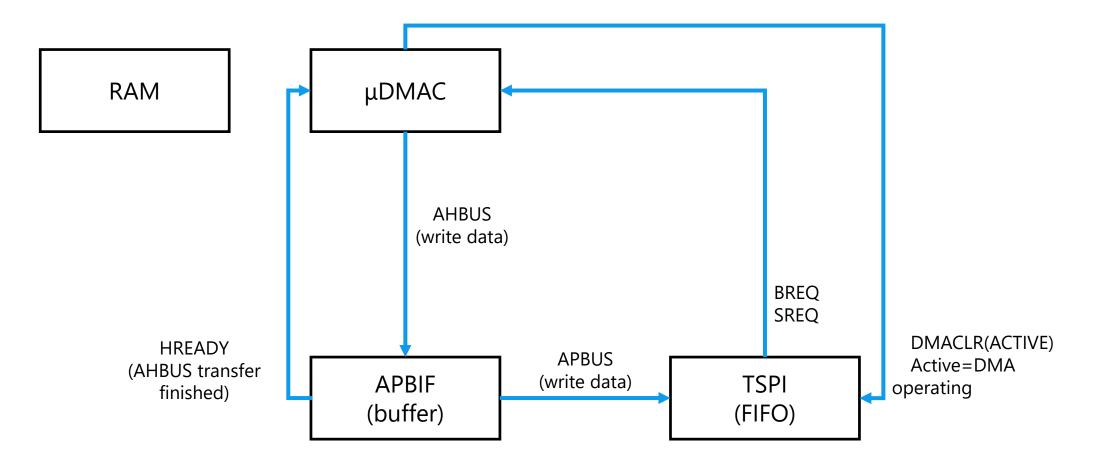

## Block diagram DMAC+APBIF+TSPI

### Related block diagram

The problem will be described to next slide.

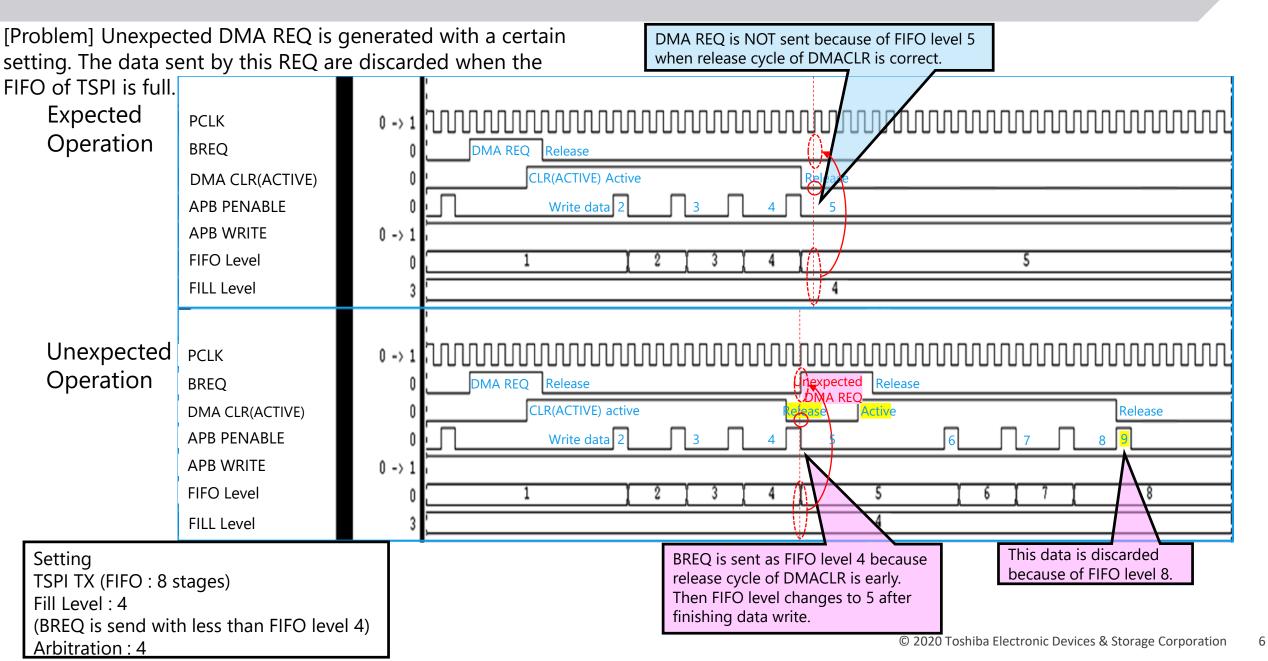

## Problem (waveform)

6

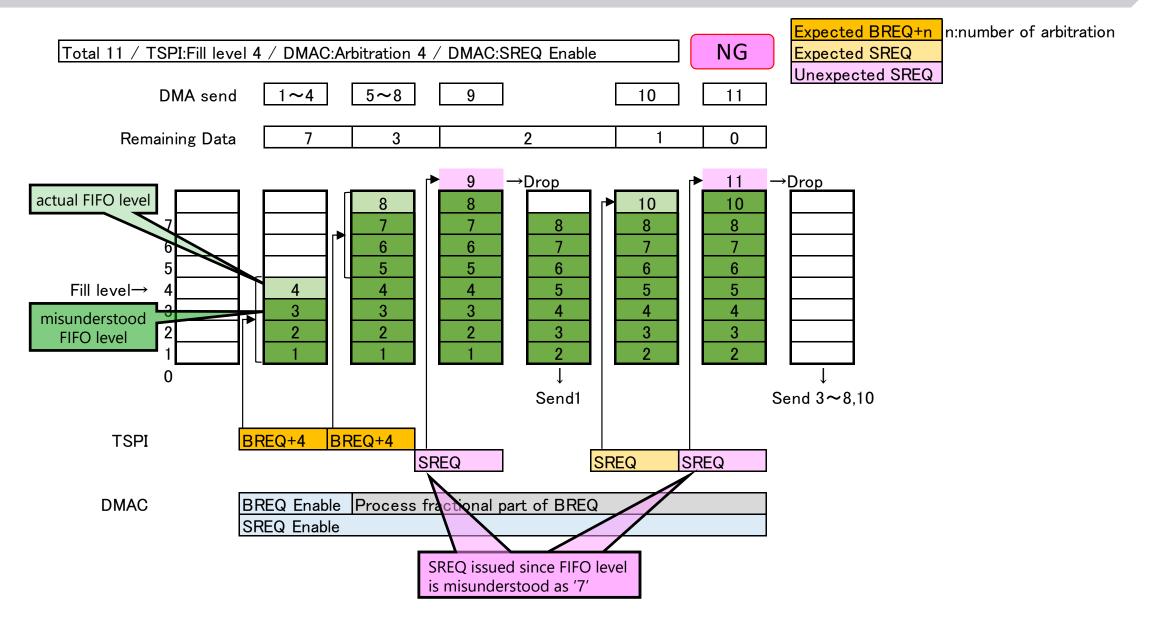

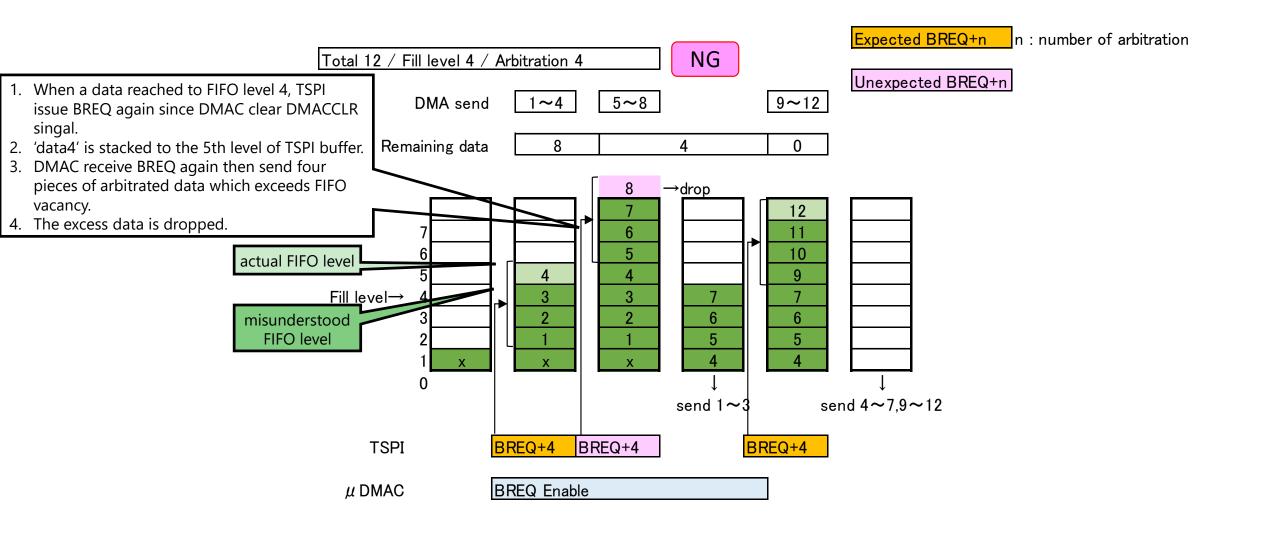

## Problematic behavior (FIFO)

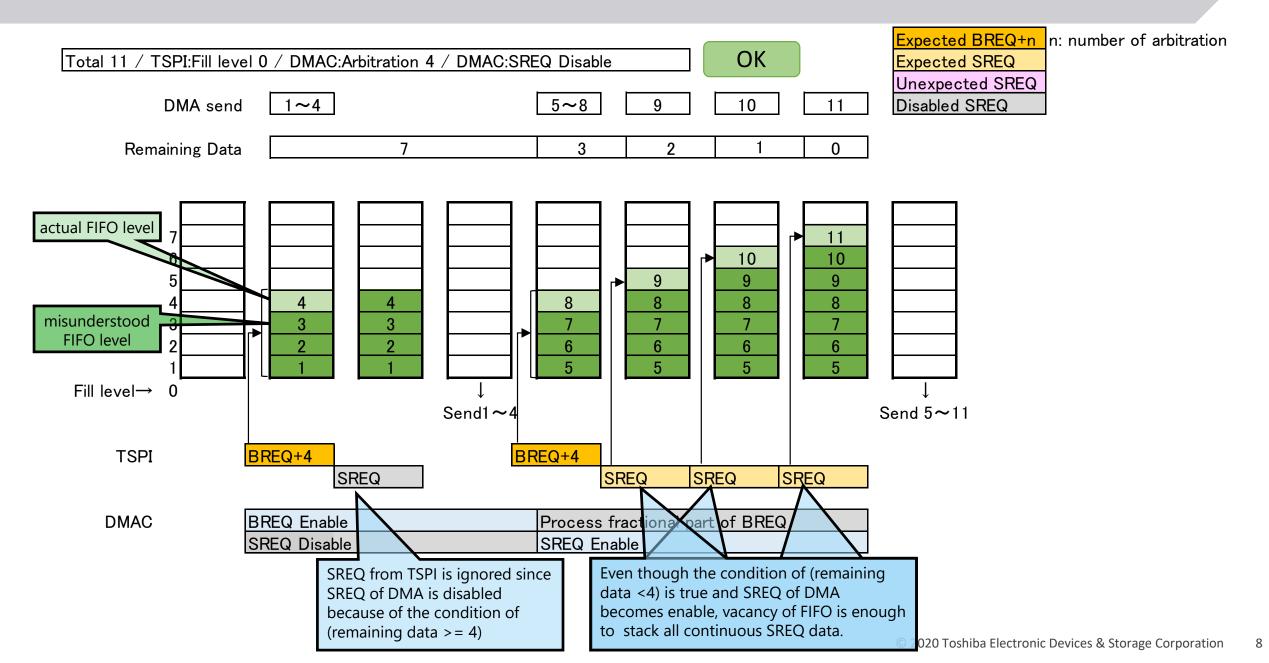

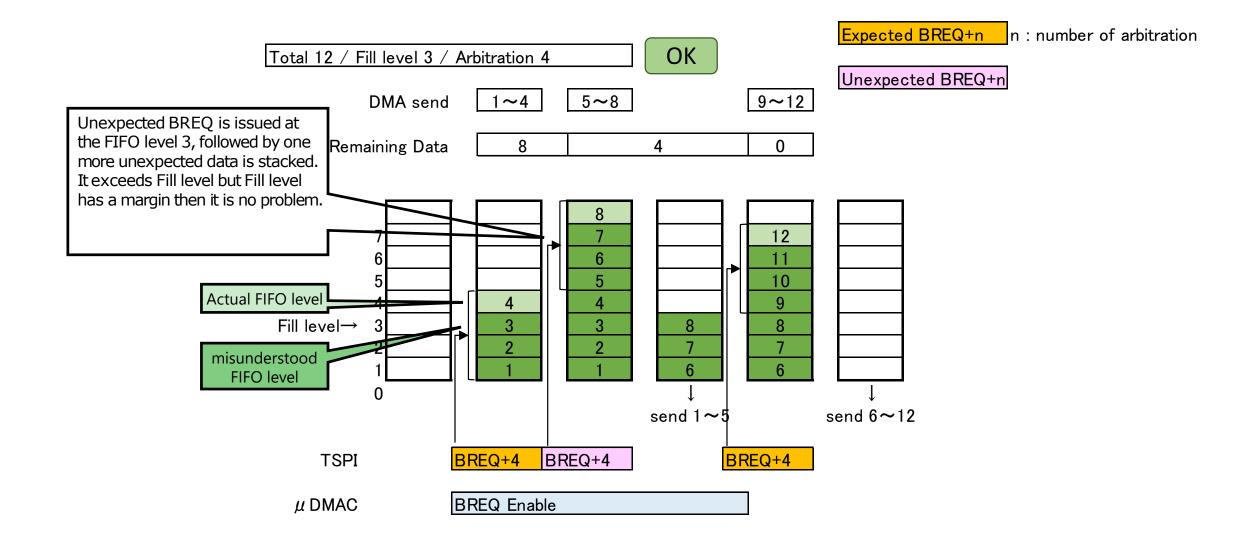

## Workaround 1: SREQ Disable / Arbitration 4 / Fill level 0

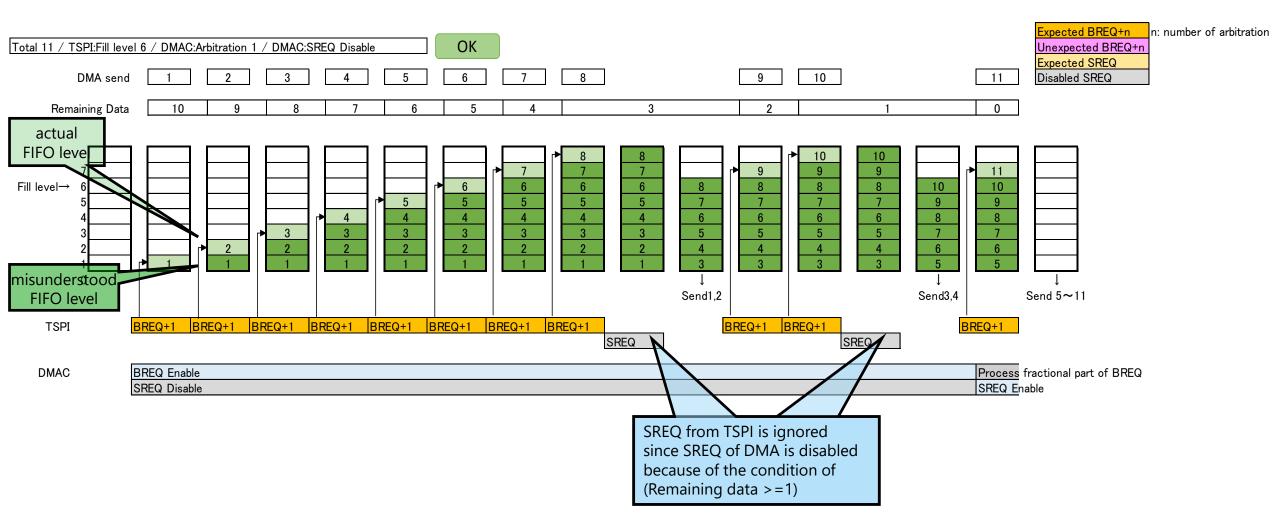

### Workaround 2: SREQ Disable / Arbitration 1 / Fill level 6

## Content to be added in the Reference Manual

| Regarding the Product Information in the Reference Manual, the items on the right will be added.                                                                                        | M3H group(1) : 2.17.6.1<br>M3H group(2) : 2.18.5.1 |  |  |  |  |                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|---------------------------------------|

| Example of TMPM3H group(2)                                                                                                                                                              | M4K group(1) : 2.6.7.1<br>M4K group(2) : 2.17.5.1  |  |  |  |  |                                       |

| 2.18.5.1 Notice when performing TSPI transmission using DMA                                                                                                                             |                                                    |  |  |  |  |                                       |

| When performing TSPI transmission using the DMAC, set the DMAC and TSPI to $(1)$ or $(2)$ below.                                                                                        |                                                    |  |  |  |  |                                       |

| (1) Set arbitration of DMAC to once<br>DMAC :                                                                                                                                           |                                                    |  |  |  |  |                                       |

| <ul> <li>Write "0000" to the Transfer mode setup(DMAChnlCfg)<r_power> in the Channel control data to</r_power></li> </ul>                                                               |                                                    |  |  |  |  |                                       |

| set arbitration to 1.<br>• Write "1" to the bit of the corresponding of the <i>[DMAxChnlUseburstSet]</i> to disable the single                                                          |                                                    |  |  |  |  |                                       |

|                                                                                                                                                                                         |                                                    |  |  |  |  | transfer request operation.<br>TSPI : |

| • set [TSPIxCR2] <til[3:0]> as below</til[3:0]>                                                                                                                                         |                                                    |  |  |  |  |                                       |

| 7-16bit: set the Fill level less or equal 6                                                                                                                                             |                                                    |  |  |  |  |                                       |

| 17-32bit: set the Fill level less or equal 2                                                                                                                                            |                                                    |  |  |  |  |                                       |

| (2) Set arbitration of DMAC to more than once<br>DMAC :                                                                                                                                 |                                                    |  |  |  |  |                                       |

| Write "0001"(twice) or "0010"(4 times) to the Transfer mode setup(DMAChnlCfg) <r_power chapped="" control="" data<="" td="" the=""><td>er&gt; in</td></r_power>                         | er> in                                             |  |  |  |  |                                       |

| <ul> <li>the Channel control data.</li> <li>Write "1" to the bit of the corresponding channel of the [DMAxChnlUseburstSet] to disable the single transfer request operation.</li> </ul> |                                                    |  |  |  |  |                                       |

| TSPI :                                                                                                                                                                                  |                                                    |  |  |  |  |                                       |

| • set [TSPIxCR2] <til[3:0]> as below</til[3:0]>                                                                                                                                         |                                                    |  |  |  |  |                                       |

| $Fill \leq FillMax - (arbitration \times 2 - 1)$                                                                                                                                        |                                                    |  |  |  |  |                                       |

| 7-16bit: FillMax = 7                                                                                                                                                                    |                                                    |  |  |  |  |                                       |

| 17-32bit: FillMax = 3                                                                                                                                                                   |                                                    |  |  |  |  |                                       |

### M3H group (1)

TMPM3H6FSFG, TMPM3H6FUFG, TMPM3H6FWFG, TMPM3H5FSFG, TMPM3H5FUFG, TMPM3H5FWFG, TMPM3H4FSUG, TMPM3H4FUUG, TMPM3H4FWUG, TMPM3H2FSDUG, TMPM3H2FUDUG, TMPM3H2FUQG, TMPM3H2FWDUG, TMPM3H2FWQG

### <u>M3H group (2)</u>

TMPM3HQFDFG, TMPM3HQFYFG, TMPM3HQFZFG, TMPM3HPFDFG, TMPM3HPFYFG, TMPM3HPFZFG, TMPM3HNFDDFG, TMPM3HNFDFG, TMPM3HNFYFG, TMPM3HNFZFG, TMPM3HMFDFG, TMPM3HMFYFG, TMPM3HMFZFG, TMPM3HLFDUG, TMPM3HLFYUG, TMPM3HLFZUG, TMPM3H2FSQG,

### M4K group(1)

TMPM4K4FSAFG, TMPM4K4FSAUG, TMPM4K4FUAFG, TMPM4K4FUAUG, TMPM4K4FWAFG, TMPM4K4FWAUG, TMPM4K4FYAFG, TMPM4K4FYAUG, TMPM4K2FSADUG, TMPM4K2FUADUG, TMPM4K2FWADUG, TMPM4K2FYADUG, TMPM4K1FSAUG, TMPM4K1FUAUG, TMPM4K1FVAUG, TMPM4K0FSADUG

#### M4K group (2)

TMPM4KQFDFG, TMPM4KQFWFG, TMPM4KQFYFG, TMPM4KPFDDFG, TMPM4KPFWDFG, TMPM4KPFYDFG, TMPM4KNFDDFG, TMPM4KNFDFG, TMPM4KNFWDFG, TMPM4KNFWFG, TMPM4KNFYDFG, TMPM4KNFYFG, TMPM4KMFDDFG, TMPM4KMFDFG, TMPM4KMFWDFG, TMPM4KMFWFG, TMPM4KMFYDFG, TMPM4KMFYFG, TMPM4KLFDFG, TMPM4KLFDUG, TMPM4KLFWFG, TMPM4KLFWUG, TMPM4KLFYFG, TMPM4KLFYUG

# Our semiconductor and storage products will always be a driving force to change the world

Toshiba Electronic Devices and Storage, together with our customers, will accelerate our future journey.

We aim to be a company that will be chosen

for our pioneering technology and spirit embedded in our products.

## **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. **TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.**

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative or contact us via our website.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

To: Distributors

# Product defect related to Serial Periferal Interface (TSPI) utilize DMA Controler (DMAC)

## TOSHIBA

2020/May/28

Toshiba Electronic Devices & Storage Corporation

Toshiba Electronic Device Solutions Corporation

Thank you for using Toshiba microcontrollers.

In the data transfer of DMAC + TSPI, a problem was found that some data was discarded.

This document will address the phenomenon and workaround.

We apologize for any inconvenience, but we ask that you review the content. If you have any questions about this matter, please contact our sales representative.

## Technical terms explanation

| The function     | Technical Terms             | The explanation                                                                                                                                                                                                                                                                        |

|------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Related Function |                             | μDMAC, APB Interface, TSPI                                                                                                                                                                                                                                                             |

| TSPI             | TSPI                        | Toshiba Serial Peripheral Interface                                                                                                                                                                                                                                                    |

|                  | FIFO                        | Transmit/Receive FIFO 8 stage (7 to 16-bit), 4 stage(17 to 32-bit)                                                                                                                                                                                                                     |

|                  | BREQ, SREQ                  | DMA Request<br>BREQ(Burst transfer request) cab transfer multiple data with one request.<br>(Number of transfers depends on DMA settings register.)                                                                                                                                    |

|                  | Fill level (n)              | DMA Transmit : BREQ and SREQ are generated when FIFO level N and under.<br>SREQ will occur if there is FIFO space.                                                                                                                                                                     |

| μDMAC            | μDMAC                       | DMA controller                                                                                                                                                                                                                                                                         |

|                  | Arbitration                 | Arbitration interval = Number of transfer when BREQ occurs.                                                                                                                                                                                                                            |

|                  | Single-transfer is disabled | DMAC can ignore SERQ when burst transfer is possible by single-transfer is disable.<br>However, if the remaining transfer count is a fraction less than the burst transfer count, single transfer is automatically enabled.                                                            |

| APB Interface    | Write-buffer                | The bus arbitration circuit between AHB and APB bus has a single-stage write buffer.<br>The DMAC releases the AHB bus first when write to the write buffer is completed.<br>After that, DMAC writes to the APB bus.<br>* There is a time lag between DMAC and peripheral write timing. |

[ Applicable products ]

TMPM066FWUG

[ Configuration that occur ]

Combination of  $\mu$ DMAC + APBIF + TSPI

[ Phenomenon ]

When transmitting data to TSPI using the DMAC, FIFO control may not be performed correctly depends on the DMAC and TSPI setting conditions, and the data transferred by the DMAC to the TSPI may be discarded.

The following page shows the check flow of the occurrence conditions.

#### CONFIDENTIAL

## Block diagram µDMAC+APBIF+TSPI

### Related block diagram

The problem will be described to next slide.

## Problem (waveform)

## Problematic behavior (FIFO)

## Workaround: case of Fill $\leq$ FIFOMax – (arbitration + 1)

CONFIDENTIAL

## Content to be added in the Reference Manual

The below will be added to the Reference Manual.

### 2.1.7.1 Notice when performing TSPI transmission using µDMAC

When performing TSPI transmission using the DMAC, set the DMAC and TSPI as below.

µDMAC:

• Write to the Transfer mode setup(DMAChnlCfg)<R\_power> in the Channel control data to set arbitration.

<R\_power> = "0000", "0001", or "0010" Arbitration = once, twice, or four times

TSPI :

set <TIL[3:0]> of [TSPIxCR2]register as below.

```

Fill \leq FIFOMax – (arbitration + 1)

```

# Our semiconductor and storage products will always be a driving force to change the world

Toshiba Electronic Devices and Storage, together with our customers, will accelerate our future journey.

We aim to be a company that will be chosen

for our pioneering technology and spirit embedded in our products.

## **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. **TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.**

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative or contact us via our website.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.